It will be Q3 when you are launching your server parts .. I sincerely hope Hans will get the "final data" already in Q2 with Zambezi's launch. Or are you going to switch departments in Q2 ? ;-)))

You mean beefy like in the sense that you would have to ask your hyperthreaded friend to help you eating up the bloody, beefy steak, because otherwise you wouldn't be able to swallow it alone ? No good idea ... because that just would leave you fighting for the beefiest pieces and in the end you would end up still being hungry, because one big steak is still too small to feed 2 beefy guys .. no good idea at all

Furthermore, the biggest car engine is useless without fuel ... think about data as fuel and Caches as fuel tank and RAM memory as gas stations (because it is comparatively quite far away ;-)).

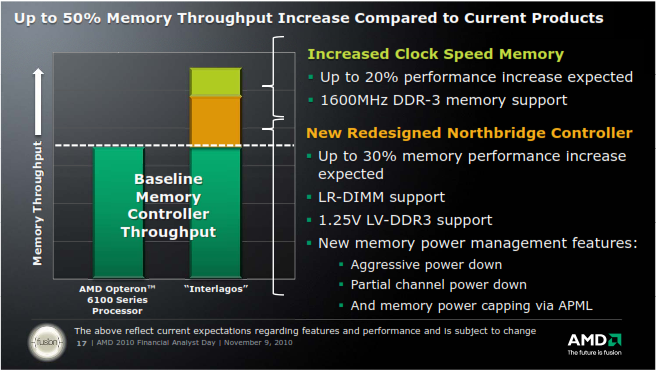

Actually ... the BD's IMC is new:

and Triple channel ist due in 2012 with the next gen bulldozers. At least for servers .. no clue about desktops. The new chips will have PCIe links, too, thus they might be compatible to Llano's Fusion socket. Other possibility would be a socket 1366/1356 competitor, e.g. a socket AM3++ with Triple channel for enthusiast. Not sure if that market would be big enough for AMD, though.

1 module = 2 Cores more plus PCIe. That has to be enough .. it will be around Thuban's die size, probably bigger .. not cheap to produce something like that.i wonder how many extra cores they could add if they would use a reworked imc with 3 channels, couldnt they add 2 or 4 more cores and remove cache, keeping it at the same die size?

BUT: Desktop users will get a 4 module version (Komodo), 5 modules are for servers, only (Sepang).

The other solution would be to let them face the center of the whole die ... so you think that would be a better idea to let 4 FPUs heat up the die's center ? ;-)and im curious, is it really ok to move the fpus and io directly towards the edge of the chip? cause those are some of the hottest parts of the chip, right? if those are at the far edge of the chip proper ihs bonding is really crucial, and the thermal stress on the outer rings of solder balls must be pretty high

Yes, but only for servers, see above.

@Hans:

Can you identify the blocks left of the decoders ? BTBs / ITLBs / something else ?

Thanks

Reply With Quote

Reply With Quote

Bookmarks