Driving strength is set for the ICs. 6/8 usually works by default. To adjust you either increase clk drive/decrease dq drive or decrease clk drive/increase dq drive, but you need to change DLL models too when doing this.

On my DDR2 G.Skill 1100mhz 2x2gb sticks I've found the best combo for me is, in the format CK Drv/DQ Drv/Dll 1/Dll 2

3/8/5/5 or 4/7/6/6.

Drive strength is the amplitude the clock out and data out are driven at within the DDR delay locked loop relevant to clock in, and out for ddr mux.

MCH Vref are set with respect to the difference default.

Vref1=00h, Vref2=00h, Vref3=80h.

The represent voltage reference points at voltage crossing. You adjust them to the same ratio they are set. ie, Vref1=05h, Vref2=05h, Vref3=85h.

Unless you understand what they do stick to this.Also you can benefit from adjusting MCH slew rate offset, and MCH ROn/Rtt.

Ie.

MCH Rtt = 06h, MCH ROn = 03h, MCH Slew rate = 0Ah, MCH Vref1 = 18h, MCH Vref2 = 18h, MCH Vref3 = 98h

I'm pretty certain that Rtt = 1/2 ROn when setting it, since Rtt is usually 2 * ROn impedance. ie Rtt = 120 ohms, Ron = 60 ohms.

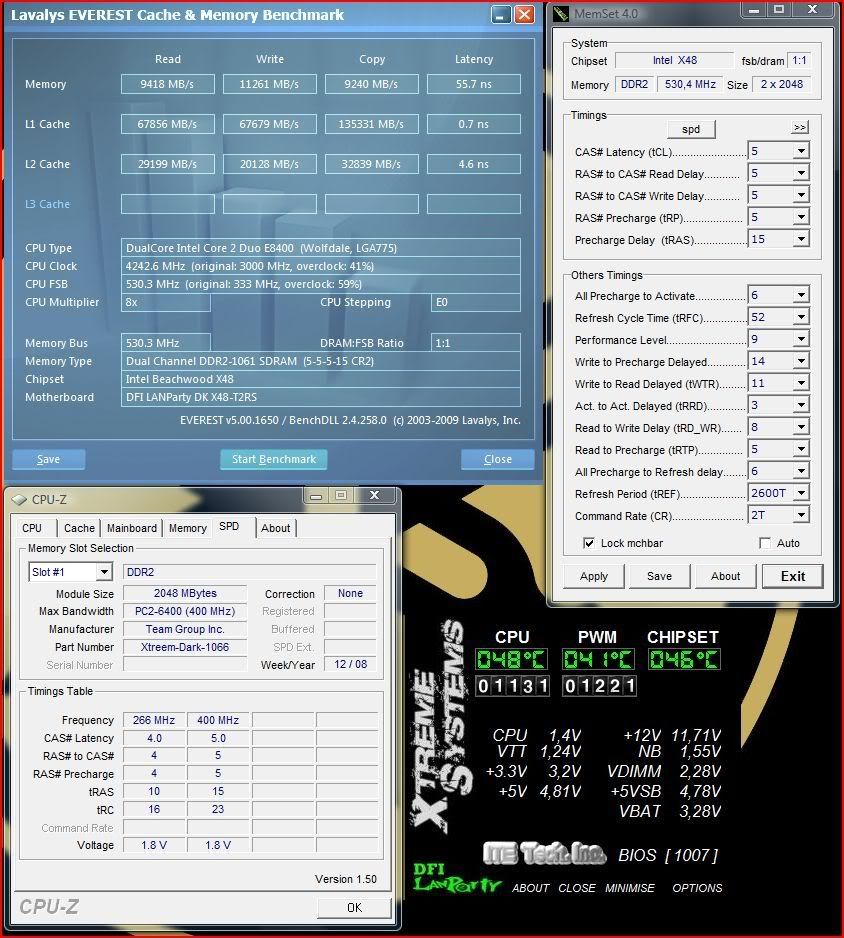

). I own an 8400 and a 2x2 kit, temgroup Xtreem, max memtest on this mobo 550

). I own an 8400 and a 2x2 kit, temgroup Xtreem, max memtest on this mobo 550  .

.

Reply With Quote

Reply With Quote

Bookmarks