gpu does not connect by hypertransport.

http://www.theregister.co.uk/2010/02..._chip_preview/

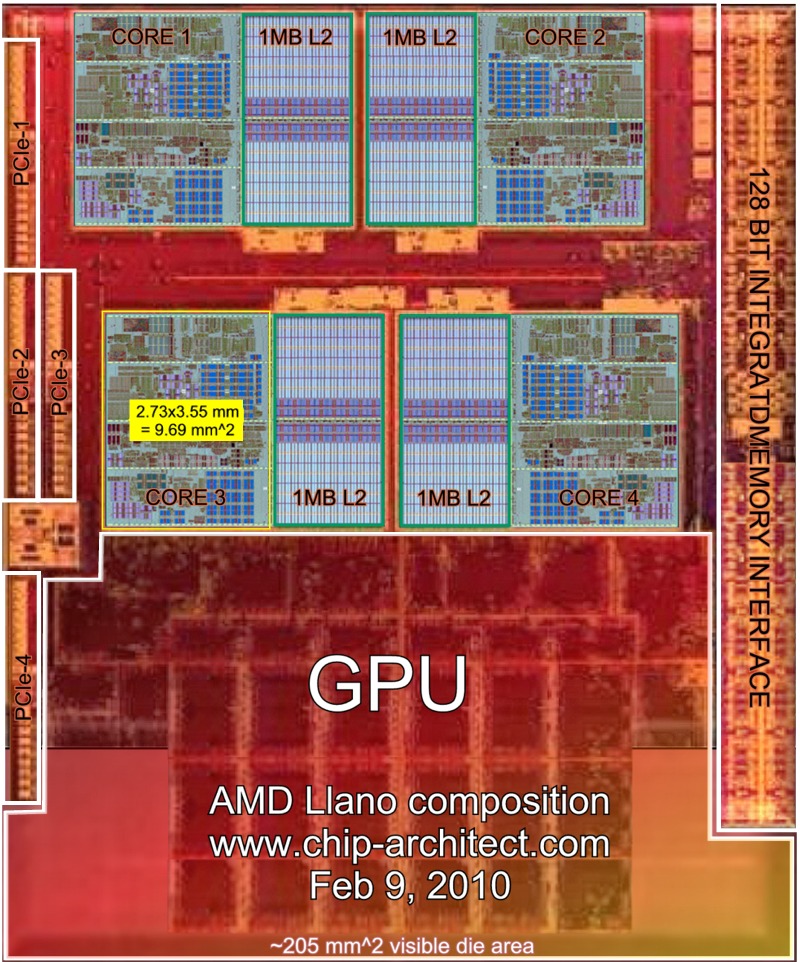

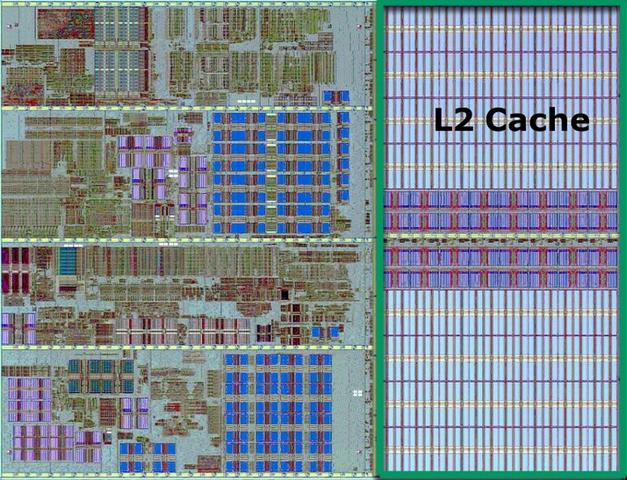

According to Sam Naffziger, a senior fellow at AMD, the Llano chip will use a 32 nanometer silicon-on insulator process and will have an on-chip DDR3 main memory controller as well as four cores and a DirectX 11 compatible GPU on the die. Naffziger would not divulge the feeds and speeds of the graphics unit, but he said that the GPU is a derivative of the current Radeon HD5000 series and that it will not link to the cores through a HyperTransport link. Instead, it will use a more direct link on the die. The architectural specifics of that link are not being discussed today at ISSCC.

Reply With Quote

Reply With Quote

.

.

Bookmarks