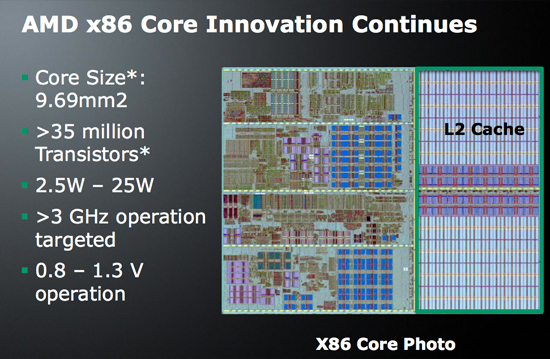

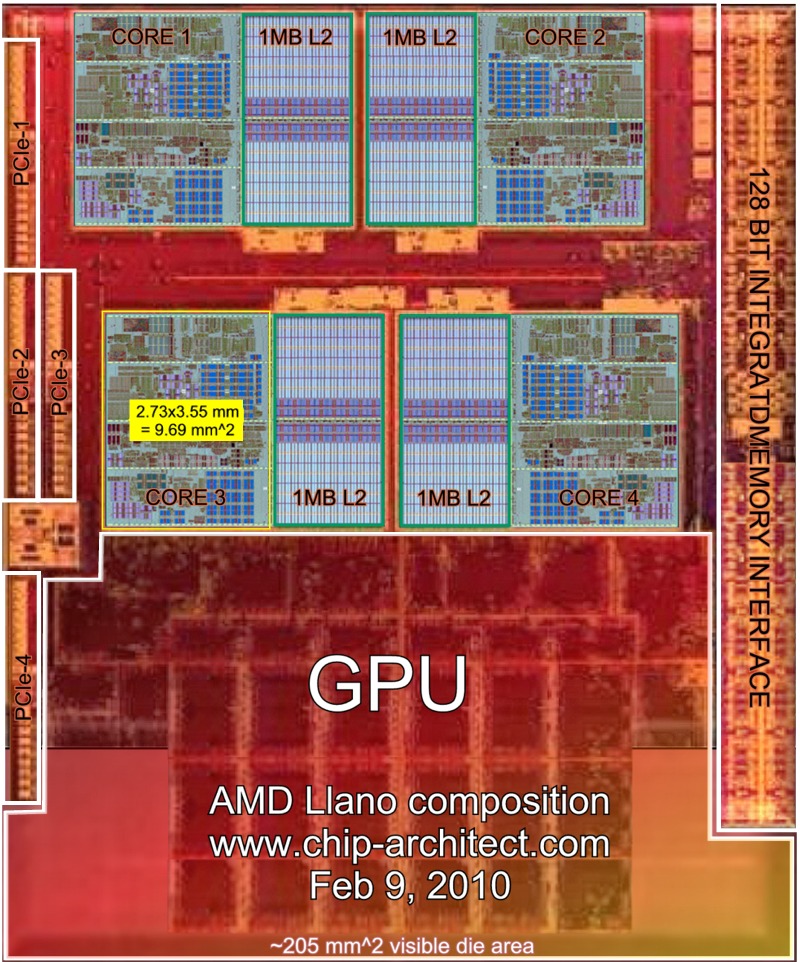

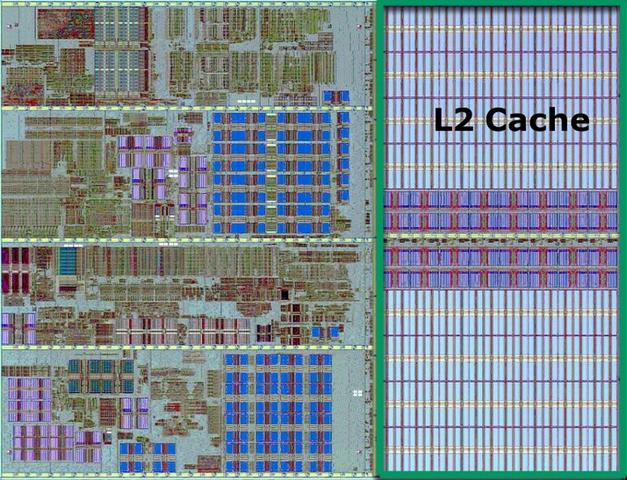

Core = 9.69mm^2

Core + L2 ~ 1.5x of that? = ~15mm^2

So basically quadcore logic under 90mm^2 (+IMC,HTPad...)?

IMO the total die size should be 140-180mm^2 or so, but no longer do they have to sell it at $99- fetching double the price should be easy, not that it would be a good purchase for desktop.

For laptops though I think this should be their way in, especially with the emphasis on power management- seems to me that this is a laptop oriented design for the most part, being able to target $300+ ASPs that AMD could previously only dream about.

Reply With Quote

Reply With Quote

.

.

Bookmarks