Note the

key word in AT's

speculative article:

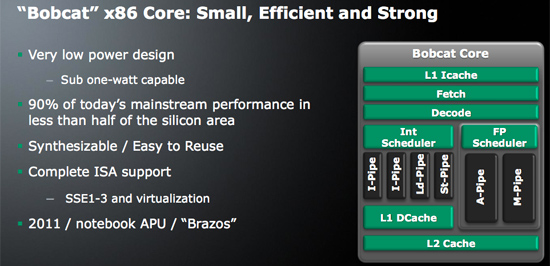

In other words he presumes. You have a diagram from AMD stating 4 pipelines(non segmented into ALUs and AGUs). I'm not saying it's 4 issue being made of grouped 4 ALUs/AGUs ,it may be 2 issue with throughput of 4 issue(look at dresdenboy's blog),but I'm still sticking to the image and the post analyst call interview with Rick Bergam who stated that each core inside the module is a 4 issue core.

PS Note that in the diagram of 10h you posted,the ALUs and AGUs are grouped together,in pairs... 3 issue made up of 3 groups of ALUs and AGUs. Very same methodology may apply to BD cores

.

.

.

Reply With Quote

Reply With Quote

Bookmarks