Max FSB Ive seen is 607 on air, 670 with CPU on LN2 (or DICE, can't remember now).

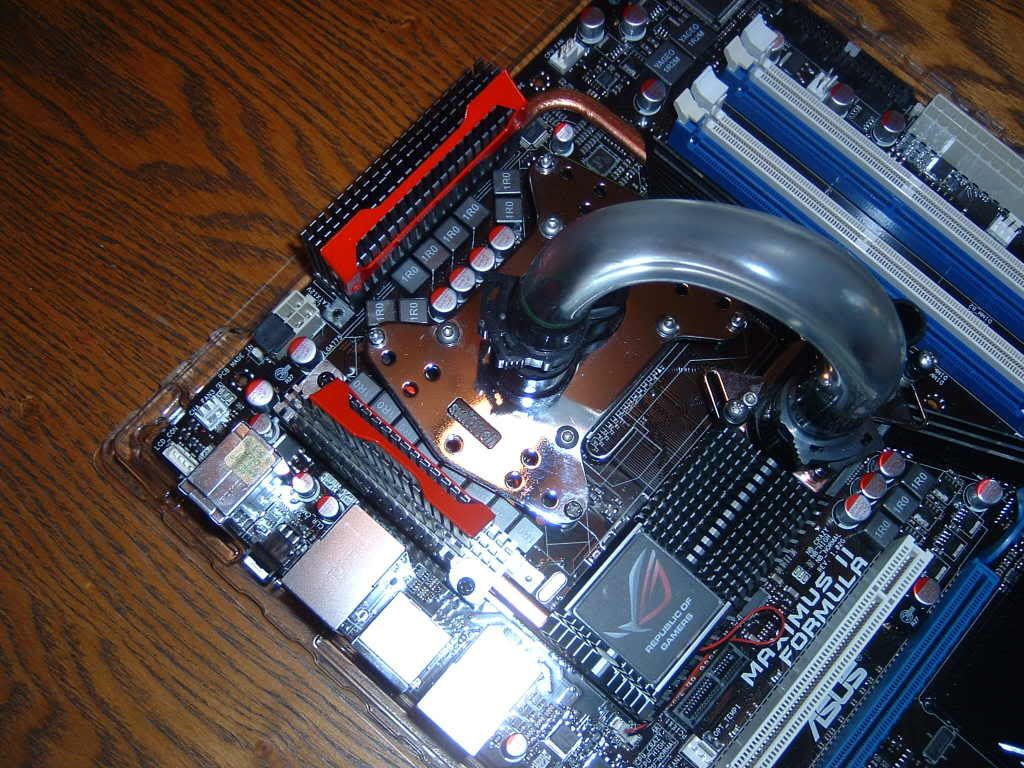

The MCW30 will fit, but fits better if you mod it slightly. Theres pics in the thread somewhere. The MCW-NBMAX is made for this board (and the rampage extreme) so it will fit perfectly onto the existing heatpipe setup (not directly onto the nb chip) - look at the pics for an idea of the options you have.

Links to pics here:

http://www.xtremesystems.org/forums/...d.php?t=205323

Reply With Quote

Reply With Quote

I did set everything to stock timings and volts and i ran an error free orthos session for 8hrs (I was hoping this would throw errors too so i could blame the equipment!!!)

I did set everything to stock timings and volts and i ran an error free orthos session for 8hrs (I was hoping this would throw errors too so i could blame the equipment!!!)

Bookmarks