I think it's possible to run at PL 2 with very lower DDR2.

Yes it's possible.

Performance Level is at OffSet 248h bit[12-8] for Channel A and 648h bit[12-8] for Channel B.

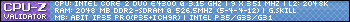

I don't know; with my IP35-PRO, if I boot with my G.Skill PC-6400 at 266Mhz, I got PL3 on channel A and PL4 on channel B...

It's the same with Read Delay Phase Adjust.

Is timings on Channel A & B are the same?

I don't understand? if you change a timing with memset and click on Apply, the timing is changed immediately.

You can check it with Everest wich show timing in real time.

Yes, it's a new buid wich I add some tRFC values in this morning.

Reply With Quote

Reply With Quote

Bookmarks