Hey guys

I am at Computex right now

Here is some of the board I saw in the show (4/F Nangang)

ASUS A75

MSI A75

ECS A75 board

ASRock A75 Board

I will upload the picture to webhosting before posting

stay tuned !

Hey guys

I am at Computex right now

Here is some of the board I saw in the show (4/F Nangang)

ASUS A75

MSI A75

ECS A75 board

ASRock A75 Board

I will upload the picture to webhosting before posting

stay tuned !

Last edited by imamage; 05-30-2011 at 09:35 PM.

TFS the pics

any BD Demo over there? they say Asus would have one

keep us updated

remove pci and add more pcie- 1x slots cmon :/

The front end uses vertical multithreading. One thread per cycle.

This is how it could work from cycle to cycle:

Decode 4 instructions of thread 0

Decode 4 instructions of thread 1

Decode 3 instructions of thread 0 (some suboptimal instruction mix)

Decode 4 instructions of thread 1

Decode 4 instructions of thread 0

Decode 4 instructions of thread 0 (core 1 has to wait for memory)

Decode 3 instructions of thread 0 (suboptimal instructions)

Thanks for pics imamage

I like what I see for Llano there!

Plenty of choice, different form factors, CF support, lots of SATA

PS. One more thing I noticed on Asus A75 board is feature called GPU Boost! I wonder how much it can overclock and of that means we will have BIOS access to tweak CPU and GPU frequencies independently of each other? Anyway seems to be the case

Last edited by Lightman; 05-31-2011 at 01:10 AM.

RiG1: Ryzen 7 1700 @4.0GHz 1.39V, Asus X370 Prime, G.Skill RipJaws 2x8GB 3200MHz CL14 Samsung B-die, TuL Vega 56 Stock, Samsung SS805 100GB SLC SDD (OS Drive) + 512GB Evo 850 SSD (2nd OS Drive) + 3TB Seagate + 1TB Seagate, BeQuiet PowerZone 1000W

RiG2: HTPC AMD A10-7850K APU, 2x8GB Kingstone HyperX 2400C12, AsRock FM2A88M Extreme4+, 128GB SSD + 640GB Samsung 7200, LG Blu-ray Recorder, Thermaltake BACH, Hiper 4M880 880W PSU

SmartPhone Samsung Galaxy S7 EDGE

XBONE paired with 55''Samsung LED 3D TV

BULLDOZER?

performance lower than expected?

http://item.taobao.com/item.htm?id=10582582718

Hmnnn? System with 至尊8核电脑主机AMD FX-8110+M5A87+蓝宝石6950 2G显卡+8G/1600 .

I can smell the bullbut I can't tell where it is coming from; the site quoted or AMD, where they are laughing their heads off.

I found this article to be interesting. If bulldozer is struggling with floats, then we have trouble ahead. Integer workloads are incredibly important for many tasks, but floating point can't be ignored. Sticking these into a Cray won't be very useful with poor float performance. Any ideas why this might be the case? Mostly I'm curious as to whether this is the performance issue or the bug (or both) that they talk about. My guess is that the performance is lacking in floats due to heat. The FMAC is shared, and probably gets crispy in large workloads while integer units are more evenly distributed about the core...

Tempting to chance heh Though if the performance issue is indeed true and it's being delayed till B2, that's reason not to given the fact you wouldn't be able to exactly exchange it lol

*sigh* It'll be interesting to see what the Llano offers for performance compared to the Phenom IIs.

As for the new board pictures, it irks me that ASRock had the gall to do that -_- Rebadging the Deluxe5 as the 990FX Extreme4 is one thing, but passing it off as a Fatal1ty w/o even as much as a color change is bull :\ There is barely even a design change to the board either! STILL are using that same blasted NB heatsink that prevents the usage of the first PCIe x1 slot, with anything except a very short USB card or NIC at least! >_<

Last edited by Formula350; 05-31-2011 at 05:26 AM.

I doubt that this is a temperature problem.

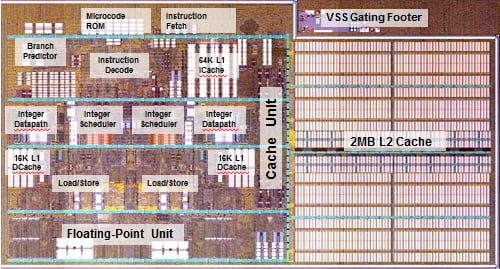

Have a look at the module:

http://www.theregister.co.uk/2011/02...er_core_isscc/

The module's two 128b FMAC units (each actually consisting of two 64b/80b FMAC units) are sitting on the left and right ends of the FPU area. You can see the split register file (bright rectangles).

So those possible hot spots are as far apart from eachother as possible in the given area - about as far as the integer execution units of both cores (in the upper parts of the int cores):

That BSN article smells of BS without the N. AMD banks on GPGPU next year,in BD+? Yeah right. BD's FPU is not weak.There may be some bug,but unless AMD totally screwed the performance estimates in their design process,there is no way the new flexfp is going to be subpar to Thuban. Also the article claims that BD is superior clock per clock than SB in integer,which is fishy to say the least.It's not impossible of course,but one would expect that 30+% IPC improvement by just going 4wide and improving prefecth is a bit on a far fetched side.

All in all,we should know more on Wednesday. AMD must correct their public roadmap if they hit a delay,there is no way around it. They did contact BSN 1 week ago and said no delay to Q2 roadmap.Now ,all of a sudden,few weeks from launch ,there are some major issues with production silicon and they need a respin.If this really was the case,AMD would have known all of this back in March or April,not 2-3 weeks before launch which is the time when product is being shipped to major resellers worldwide.

Frankly, the only weight I give to it is that he mimics that BD will be pushed out, the rest of his analysis/commentary is, at most, questionable.

Theo is not the most technically astute journalist on the net. In fact, is more often wrong than he is right. He is looking at the technical disclosures of BD and extrapolating a conclusion relative to SB based on his understanding of compute architectures of which he knows little to nothing about.

EDIT: There are really 3 tech sites that give good analysis of compute architectures -- Arstechnica, Jon Stokes -- Realworld Tech, David Kanter -- and Anandtech, Anand Shrimpi. All 3 have educational backgrounds on the subject -- as I understand it, Stokes and Kanter actually roomed together in college. I would not trust much of what Theo has to say regarding this topic.

Last edited by JumpingJack; 05-31-2011 at 07:22 AM.

One hundred years from now It won't matter

What kind of car I drove What kind of house I lived in

How much money I had in the bank Nor what my cloths looked like.... But The world may be a little better Because, I was important In the life of a child.

-- from "Within My Power" by Forest Witcraft

Last edited by JumpingJack; 05-31-2011 at 07:22 AM.

One hundred years from now It won't matter

What kind of car I drove What kind of house I lived in

How much money I had in the bank Nor what my cloths looked like.... But The world may be a little better Because, I was important In the life of a child.

-- from "Within My Power" by Forest Witcraft

Well, if that is true that puts the total die size at about 285 mm^2, which is a healthy die size (economically) for the markets it will target.

Also, the relative size of the L1 cache to L2, I recall reading they went to an 8T bit in L1 which makes sense in the die shot. Interesting.

One hundred years from now It won't matter

What kind of car I drove What kind of house I lived in

How much money I had in the bank Nor what my cloths looked like.... But The world may be a little better Because, I was important In the life of a child.

-- from "Within My Power" by Forest Witcraft

I'm calling myself out on uber-FAIL*sigh* I didn't even notice that the motherboard doesn't show any signs of "Fatal1ty" silk screening :\ Seems as though the label board above it was misplaced OR the wrong motherboard was accidentally put there instead. heh

Thar be hope off the starboard bow, ya-har!

I think the article explained it pretty well.

The interesting bit to us is that while K8/10 generation of Opterons lagged behind Intel in integer and pummeled them in Floating Point tests, the result right now is exactly the opposite: clock-by-clock, Bulldozer will walk all over Sandy Bridge in integer and get hammered in Floating Point tests. The reason for this is the fact that second generation Bulldozer (so called Bulldozer Enhanced) will unite the Bulldozer cores with Radeon HD graphics which will take over the floating point operations as much as possible through OpenCL and other GPU Computing APIs.

See I just can't see AMD making that move. There wouldn't be a huge reason for companies to use a 'Dozer in their current C32/G34 systems if they won't be an all'round upgrade for them... My understanding was the 2nd Gen chips would move over to a new socket, meaning that there really would be little reason to upgrade now when a future upgrade wouldn't even be able to utilize the same socket anymore. I mean maybe the C32 equivelant chips could move over to G34 when they get a GPU, and that'd be pretty cool, but how likely is it really? :\

And that would be the part which hints the article is BS, without the "N".

Next generation, there will be enhanced BD cores + GPU in the form of an APU, codenamed Trinity. Total replacment of FPU with a shader array is still far away, 2013 the earliest I'd say.

While I can see the issues with FP code BD might have due to having only one FP scheduelr per module and with 256bit code, it shouldn't be that bad if Cray chose them for their blades...

Phoenix Technology News May 31 News, in today's Taipei computer show, AMD senior vice president of Products Group and general manager of RickBergman dialogue with the Phoenix Science and Technology, said, Fusion will be released tomorrow in the product for the Tablet PC;

对于备受关注的Bulldozer(推土机)产品,RickBergman向凤凰网科技频道表示,该款产品 将可以在今年夏季看到。 The concern Bulldozer (Bulldozer) products, RickBergman Technology Channel to Phoenix, said a product that will be able to see this summer.

http://tech.ifeng.com/digi/special/2...744615_0.shtml

ROG Power PCs - Intel and AMD

CPUs:i9-7900X, i9-9900K, i7-6950X, i7-5960X, i7-8086K, i7-8700K, 4x i7-7700K, i3-7350K, 2x i7-6700K, i5-6600K, R7-2700X, 4x R5 2600X, R5 2400G, R3 1200, R7-1800X, R7-1700X, 3x AMD FX-9590, 1x AMD FX-9370, 4x AMD FX-8350,1x AMD FX-8320,1x AMD FX-8300, 2x AMD FX-6300,2x AMD FX-4300, 3x AMD FX-8150, 2x AMD FX-8120 125 and 95W, AMD X2 555 BE, AMD x4 965 BE C2 and C3, AMD X4 970 BE, AMD x4 975 BE, AMD x4 980 BE, AMD X6 1090T BE, AMD X6 1100T BE, A10-7870K, Athlon 845, Athlon 860K,AMD A10-7850K, AMD A10-6800K, A8-6600K, 2x AMD A10-5800K, AMD A10-5600K, AMD A8-3850, AMD A8-3870K, 2x AMD A64 3000+, AMD 64+ X2 4600+ EE, Intel i7-980X, Intel i7-2600K, Intel i7-3770K,2x i7-4770K, Intel i7-3930KAMD Cinebench R10 challenge AMD Cinebench R15 thread Intel Cinebench R15 thread

New server sockets are planned for next year, and the roadmaps shows Komodo having integrated graphics.

Look for Sepang and Terramar:

http://blogs.amd.com/work/fadcodenames/

Not that hard to put together this: even the relatively legacy free G34 can't handle the next generation CPU's, so how can anyone expect AM3+ to do it?

Why should Komodo stay with PCIe on on a separate NB? To please AM3+ owners?

http://translate.google.com/translat...545%2F&act=url

Still no one wants to believe it. "Komodo is not an APU blablabla.."

And even if there's no integrated graphics, there will be integrated PCIe for sure, which means a new socket.

I can imagine all the whining when the roadmaps for Komodo shows a new socket.

I know I'm repeating myself..

Hate to say it, but I told you so.

http://www.xtremesystems.org/forums/...5&postcount=45

Last edited by Mats; 05-31-2011 at 03:24 PM.

I was under the impression everyone knew this, bd ver 2 will have a new socket.There was a slide about it last year, cant find it now tho.

It showed "current" BD and in middle of the 2012 it was "BD ver 2" with some new socket.

And it showed integrated pcie .

BTW,

from this AMD BLOG, besides it says H1 2011 for bulldozer (may be obsolote by now).

What i find interesting is that sepang has triple channel memory ,and thats a single die socket, kind of intel 1366.Maybe theres gonna be desktopish version of that.

No IGP.“Komodo”

Market: Server and Performance Desktops

What is it? “Komodo” is AMD’s next generation CPU and is primarily intended for servers and high-performance desktops. “Komodo” will feature next-generation “Bulldozer” CPU cores and, in desktop PC platforms, is designed to couple with DirectX® 11 GPUs to provide enthusiast-level system performance.

Planned for introduction: 2012

Last edited by XRL8; 05-31-2011 at 04:05 PM.

Bookmarks