4.5 design Solutions for the Bulldozer 32nm Soi 2-core processor 3:15 pM

Module in an 8-core cpu

T. Fischer1, S. Arekapudi2, E. Busta1, C. Dietz3, M. Golden2, S. Hilker2, A. Horiuchi1, K. A. Hurd1,

D. Johnson1, H. McIntyre2, S. Naffziger1, J. Vinh2, J. White4, K. Wilcox4

1AMD, Fort Collins, CO

2AMD, Sunnyvale, CA

3AMD, Austin, TX

4AMD, Boxborough, MA

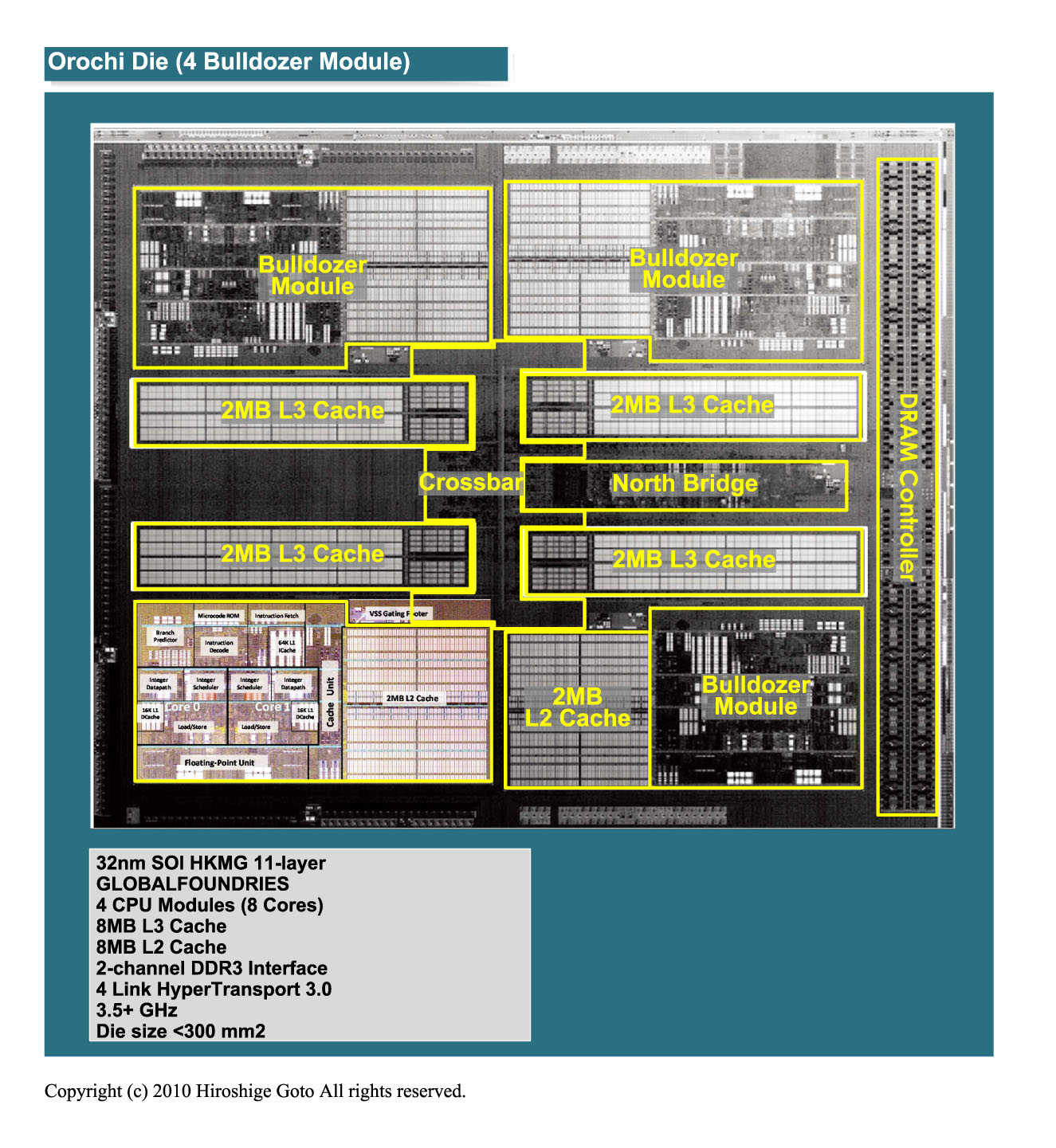

The Bulldozer 2-core CPU module contains 213M transistors in an 11-metal layer 32nm high-k metalgate

SOI CMOS process and is designed to operate from 0.8 to 1.3V. This micro-architecture improves

performance and frequency while reducing area and power over a previous AMD x86-64 CPU in the

same process. The design reduces the number of gates/cycle relative to prior designs, achieving

3.5GHz+ operation in an area (including 2MB L2 cache) of 30.9mm2.

4.6 40-entry unified out-of-order Scheduler and integer execution unit 3:45 pM

for the aMd Bulldozer x86-64 core

M. Golden, S. Arekapudi, J. Vinh

AMD, Sunnyvale, CA

A 40-instruction out-of-order scheduler issues four operations per cycle and supports single-cycle operation

wakeup. The integer execution unit supports single-cycle bypass between four functional

units. Critical paths are implemented without exotic circuit techniques or heavy reliance on full-custom

design. Architectural choices minimize power consumption.

)

Reply With Quote

Reply With Quote

, so with 32nm will see no problem

, so with 32nm will see no problem

)

)

Bookmarks