450x8.5=3.825Ghz

MB Intelligent Tweaker(M.I.T.)

Robust Graphics Booster ...............: Auto

CPU Clock Ratio .......................: 8 <===

Fine CPU Clock Ratio...................: +0.5 <===

CPU Frequency .........................: 3.825 GHz (450X8.5)

Clock Chip Control

Standard Clock Control

CPU Host Clock Control.................: [Enabled] <===

CPU Host Frequency (Mhz) ..............: 450 <===

PCI Express Frequency (Mhz) ...........: 100 <===

C.I.A.2 ...............................: [Disabled] <===

Advanced Clock Control [Press Enter]

CPU Clock Drive........................: 800mV <===

PCI Express Clock Drive................: 900mV <===

CPU Clock Skew (ps)....................: 0ps

MCH Clock Skew (ps)....................: 0ps

DRAM Performance Control

Performance Enhance....................: [Std] <===

Extreme Memory Profile (X.M.P.)........: [Disabled] <===

(G)MCH Frequency Latch.................: [400MHz] <===

System Memory Multiplier ..............: 2.0B <===

Memory Frequency (Mhz) ................: 950

DRAM Timing Selectable ................: [Manual] <===

Standard Timing Control

CAS Latency Time.......................: 5 <===

tRCD ..................................: 5 <===

tRP'...................................: 5 <===

tRAS...................................: 15 <===

Advanced Timing Control

tRRD................................(4): [AUTO]

tWTR................................(4): [AUTO]

tWR.................................(8): [AUTO]

tRFC...............................(68): [AUTO]

tRTP................................(4): [AUTO]

Command Rate (CMD) .................(0): 2T <===

Driving Strength Profiles

Driving Strength ......................: [AUTO]

Channel A

Static tRead Value..................(6): [10] <===

tRD Phase0 Adjustment..................: [AUTO]

tRD Phase1 Adjustment..................: [AUTO]

tRD Phase2 Adjustment .................: [AUTO]

tRD Phase3 Adjustment..................: [AUTO]

Trd2rd(Different Rank).................: [AUTO]

Twr2wr(Different Rank).................: [AUTO]

Twr2rd(Different Rank).................: [AUTO]

Trd2wr(Same/Diff Rank).................: [AUTO]

Dimm1 Clock Skew Control...............: [AUTO]

Dimm2 Clock Skew Control...............: [AUTO]

DDR Write Training.....................: [AUTO]

Channel B

Static tRead Value..................(6): [10] <===

tRD Phase0 Adjustment..................: [AUTO]

tRD Phase1 Adjustment..................: [AUTO]

tRD Phase2 Adjustment .................: [AUTO]

tRD Phase3 Adjustment..................: [AUTO]

Trd2rd(Different Rank).................: [AUTO]

Twr2wr(Different Rank).................: [AUTO]

Twr2rd(Different Rank).................: [AUTO]

Trd2wr(Same/Diff Rank).................: [AUTO]

Dimm1 Clock Skew Control...............: [AUTO]

Dimm2 Clock Skew Control...............: [AUTO]

DDR Write Training.....................: [AUTO]

Motherboard Voltage Control

CPU

Load-Line Calibration..................: [Enable]

CPU Vcore..............................: 1.250v <===

CPU Termination........................: 1.30 <===

CPU PLL................................: 1.57 <===

CPU Reference..........................: 0.863 <===

MCH/ICH

MCH Core...............................: 1.36V <===.

MCH Reference..........................: 0.863 <===

MCH/DRAM Ref...........................: 0.96 <===

ICH I/O................................: 1.5 <===

ICH Core...............................: 1.1 <===

DRAM

DRAM Voltage...........................: 2.1v <===

DRAM Termination ......................: 0.96 <===

Channel A Reference....................: 0.96 <===

Channel B Reference ...................: 0.96 <===

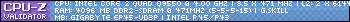

CPU = Q9550 rev C1

RAM = G.Skill PC2-8500C5 2x2048MB

PS.

If anyone can tell me the code to put this into a frane that would be helpful

@Touche

Will give your recommendations a go in a min. Thanks for your help and patience with this

Reply With Quote

Reply With Quote

Bookmarks