My rig :-

CPU: QX9770-C1 @ 4038MHz.

GPU: XFX GTX280 XT O/C. Audio: Creative X-Fi Elite Pro.

MEM: Corsair Dominator 2x1Gb TWIN3X2048-1800C7DFIN G @ 7-7-7-20 1T 1901MHz.

DRIVES: Samsung F1 1TB & 2x500Gb Hitachi SATA 2.

2xSamsung 20xDVD-RW SATA.

O/S: Vista Ultimate 32bit SP1.

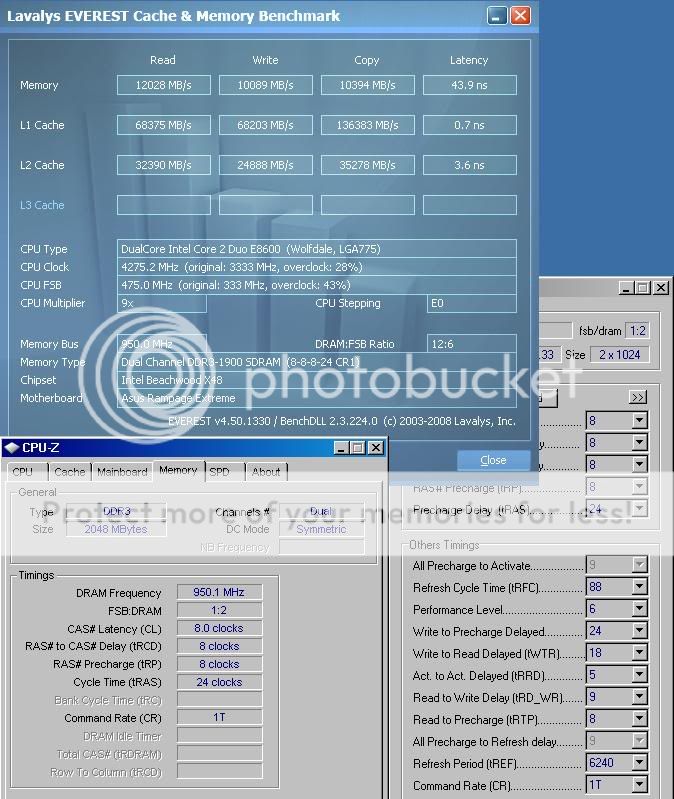

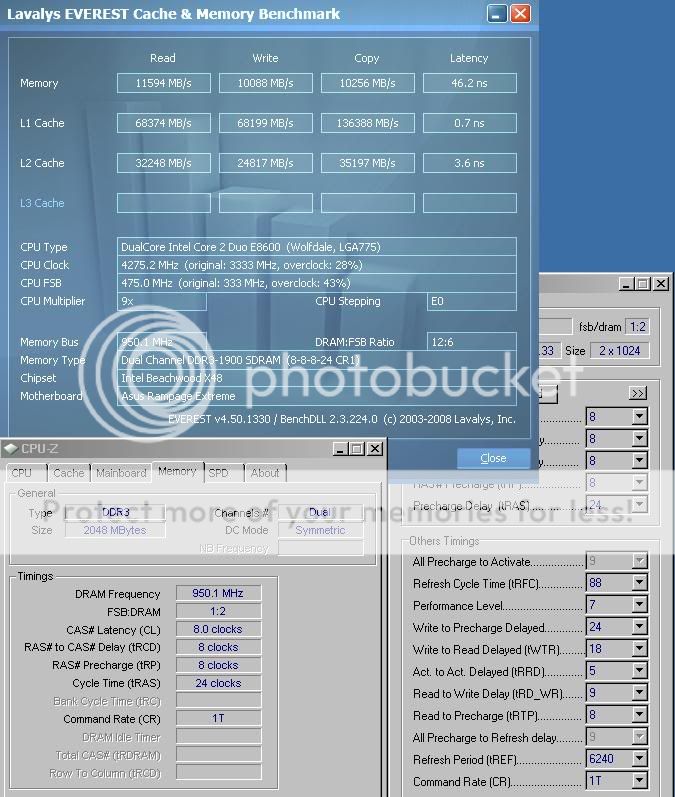

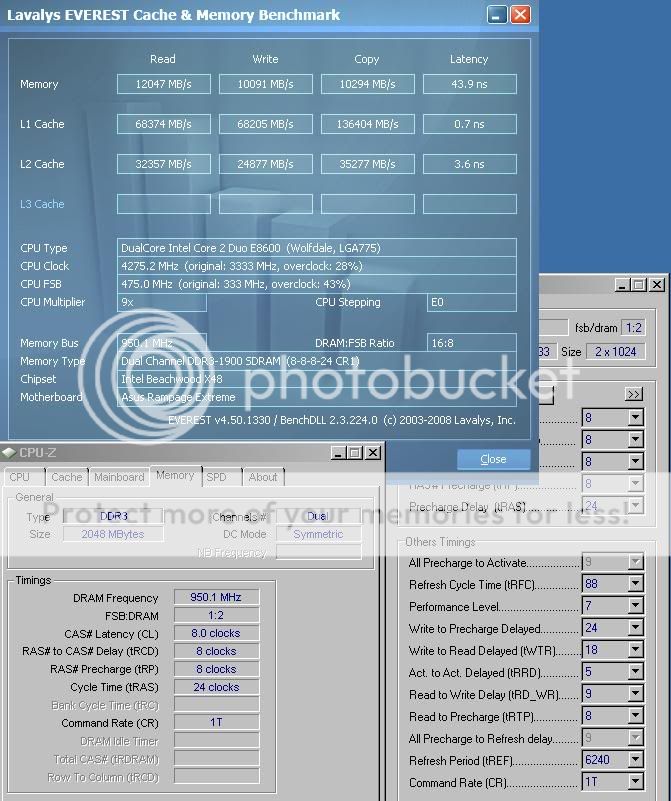

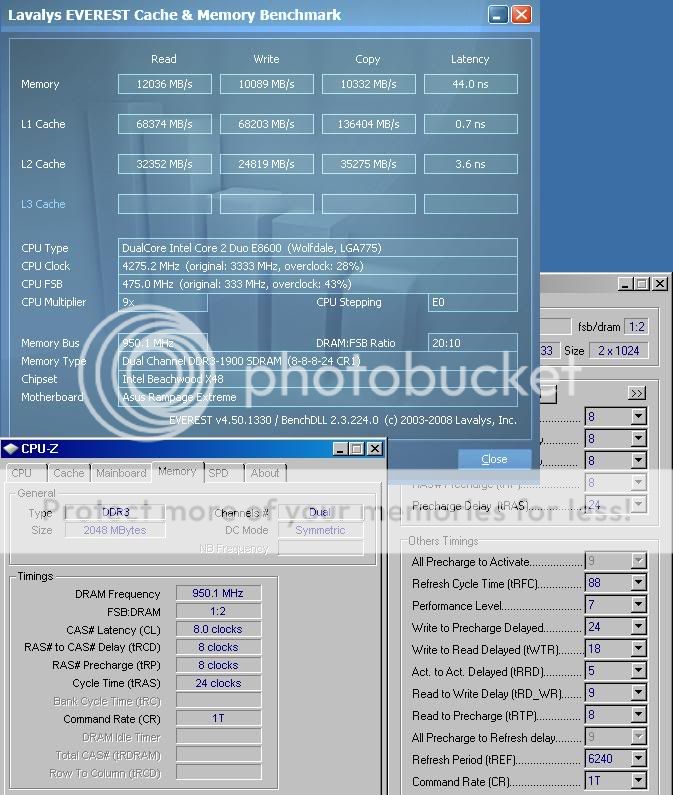

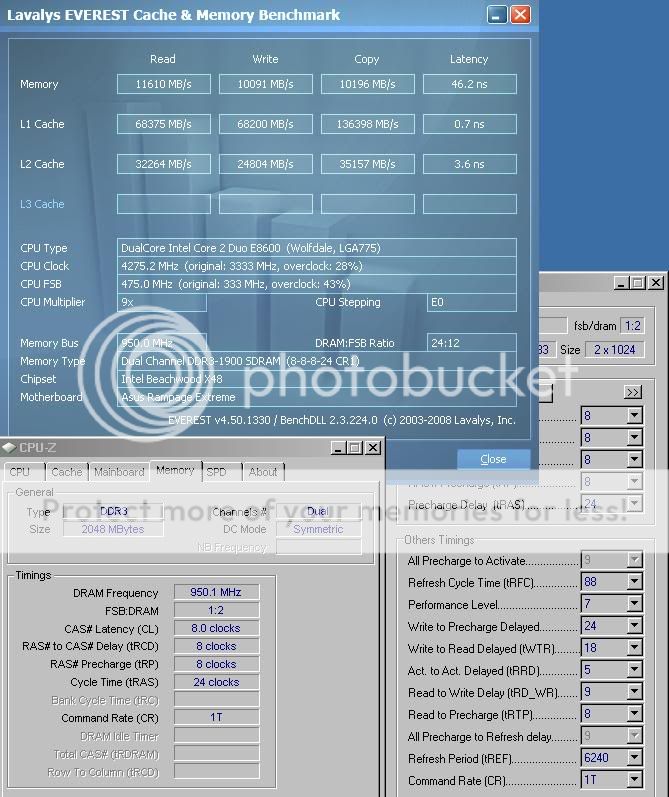

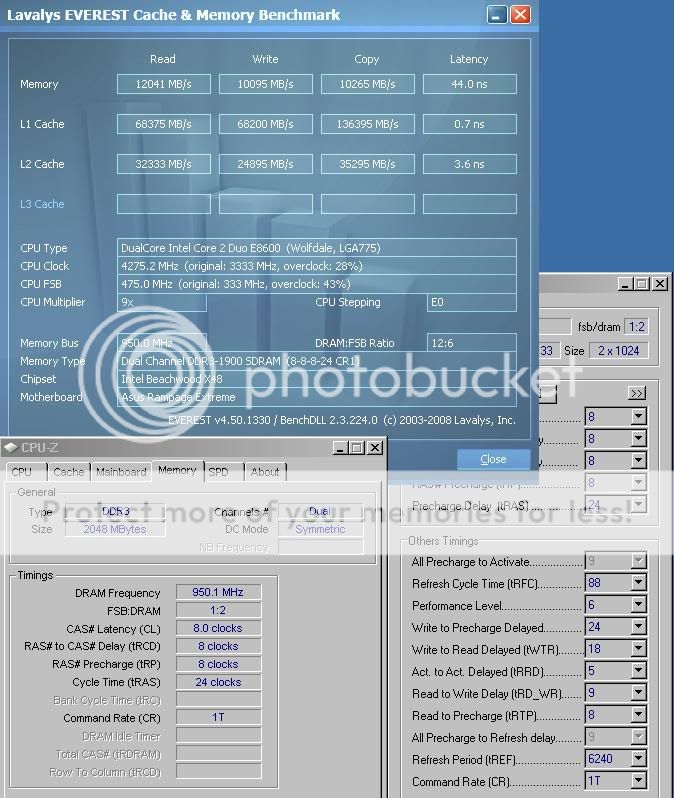

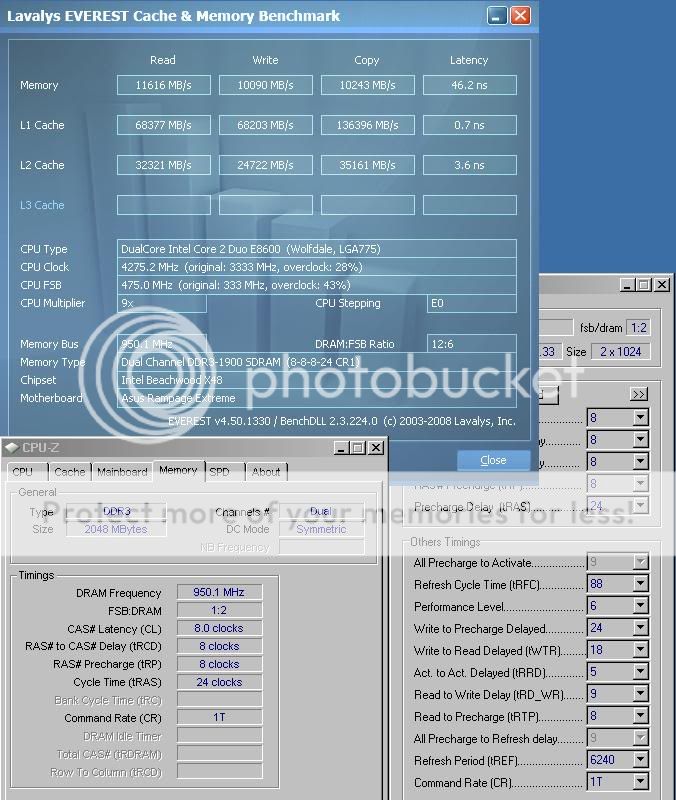

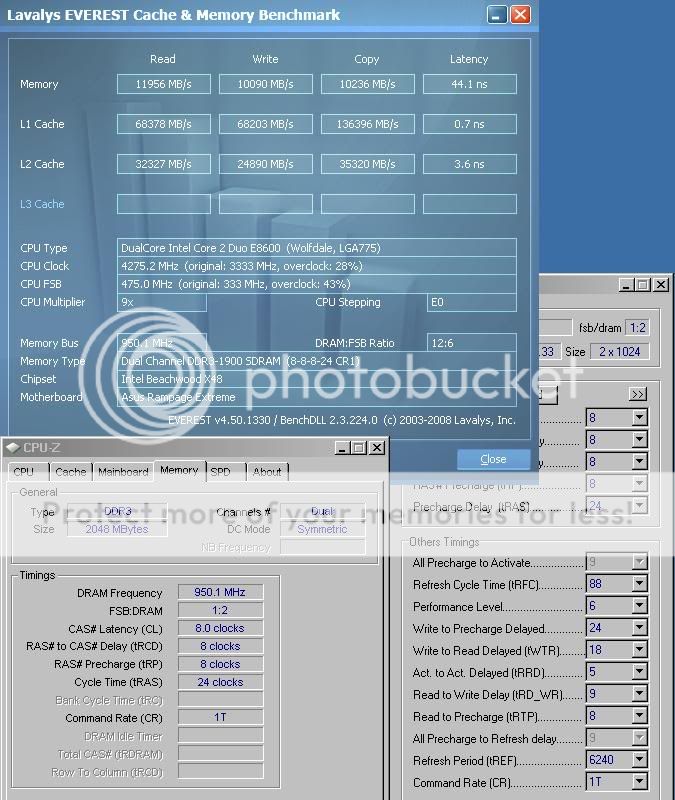

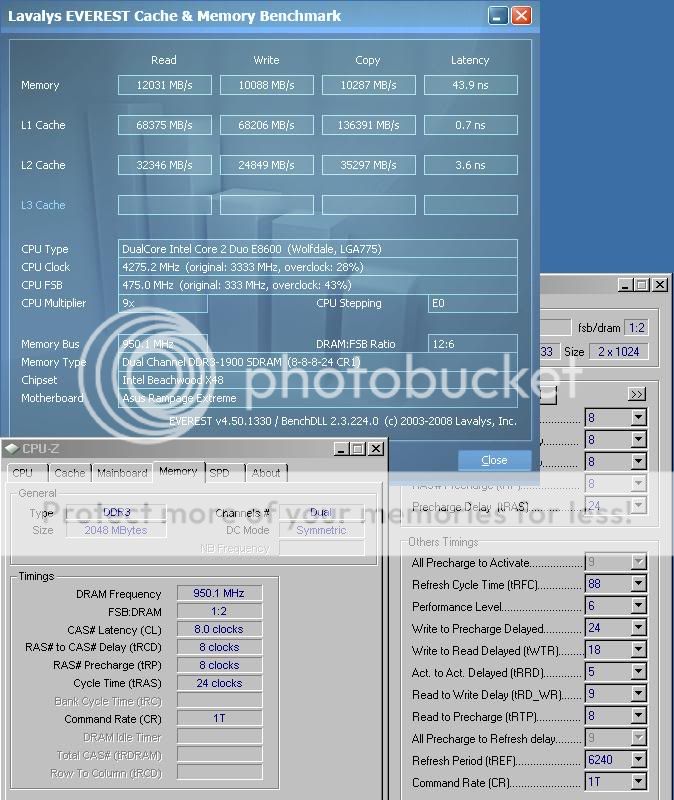

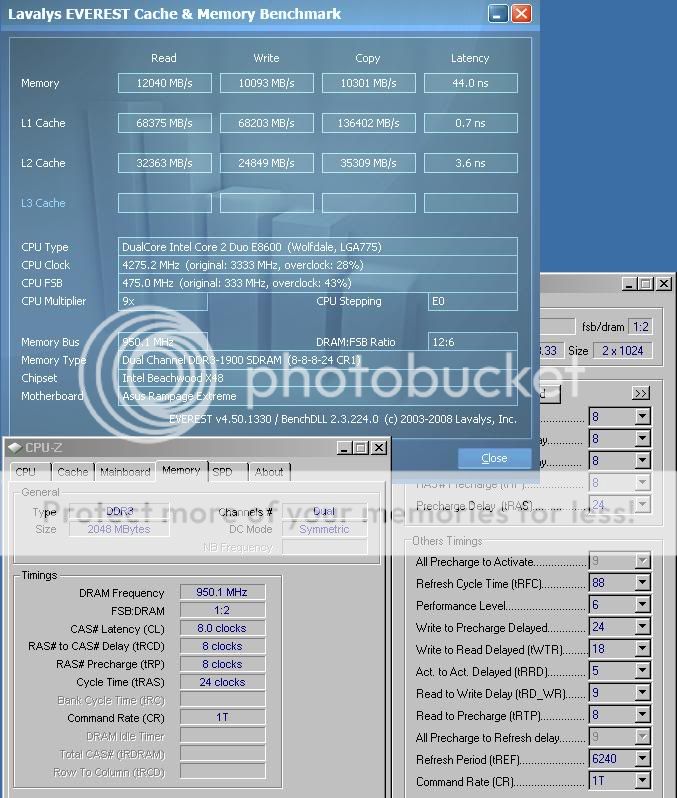

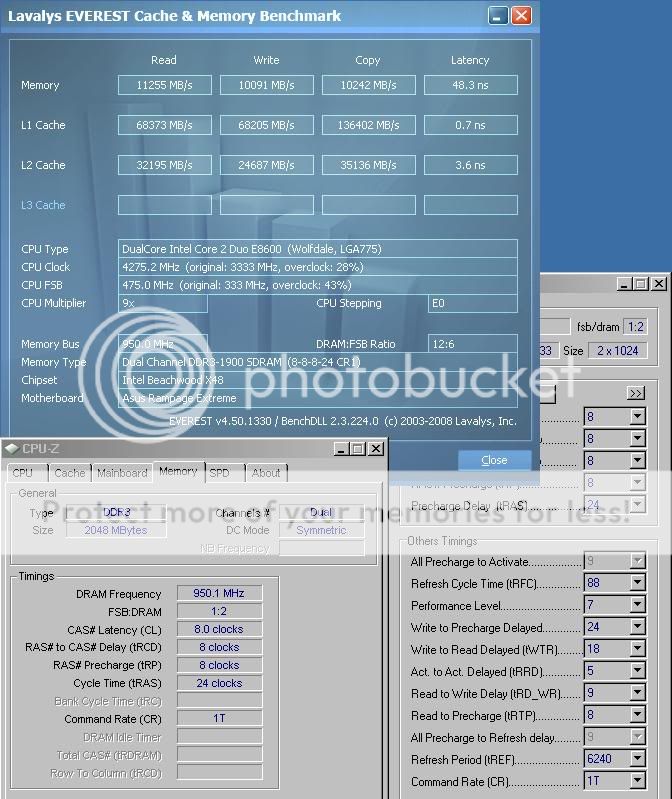

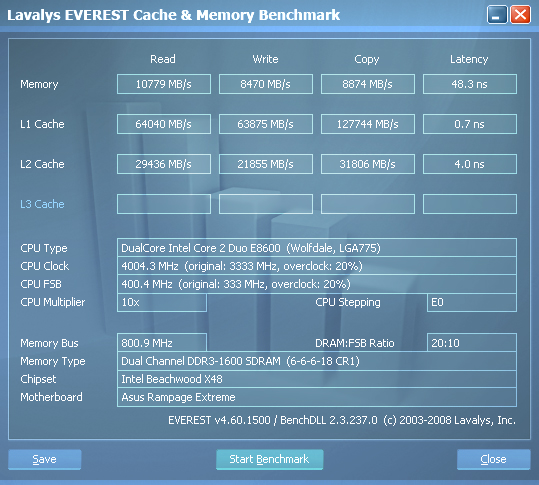

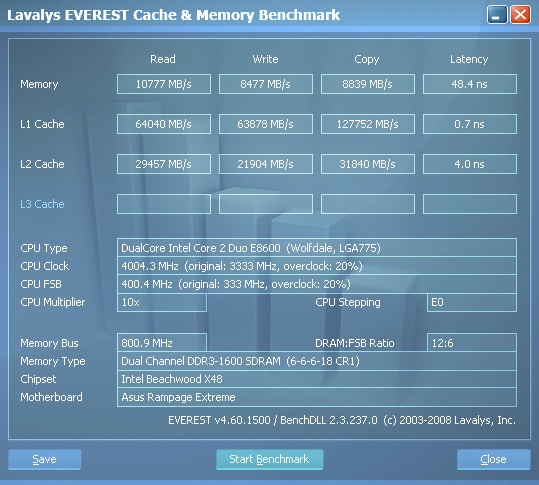

M/B: Asus Rampage Extreme. Bios : 1003.

PSU: Enermax Infinity 720w (waiting for Enermax Revolution 1050w).

CASE: CM Cosmos S RC-1100 v2.

LOOP 1: <- Black Ice Stealth 360 -> EK Multi-Opt 150 Rev2 -> Swiftech MCP655 -> Swiftech Apogee GTZ -> EK NB SMAX -> : Tygon R3603 tubing and EK barbs all 1/2in ID.

24/7 SETTINGS : FSB 475, Ratio x8.5, Strap 333, DRAM 1901 @ 2.06v, CPUv 1.47, LLC DIS, GTLs +40+40+40+40 NB +60, PLLv 1.59, VTT 1.40, NBv 1.59, SB1.5 1.58, SB1.05 1.10

Reply With Quote

Reply With Quote

, i have the rampage coming tomorrow but already have maximus extreme and the rampage has a lot more bios settings so a bit of a learning curve

, i have the rampage coming tomorrow but already have maximus extreme and the rampage has a lot more bios settings so a bit of a learning curve

s'all just trial n error and diff kits seem to like diff skews

s'all just trial n error and diff kits seem to like diff skews

Kensek

Kensek

.jpg)

Bookmarks