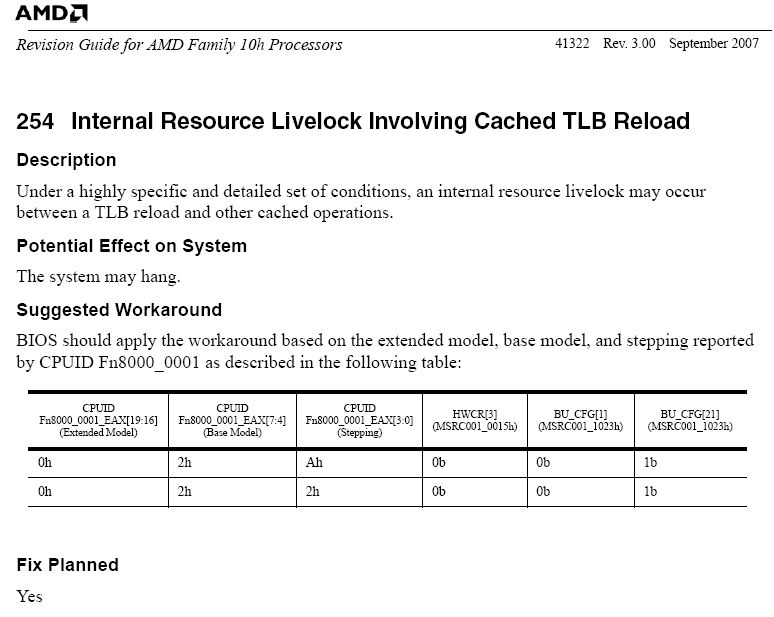

The new K10 has two Erratas related to TLB caching.

The first errata #254 is already docuentend in the K10 Revision Guide Version 3.0

http://www.amd.com/us-en/assets/cont...docs/41322.pdf

You can see the recommended fix is to clear the Bit Nr 3. in the MSR Register C0010015h and Bit Nr. 1. in the MSR Register C0011023h.

The second errata #298 was found short after phenoms where released. AMD prepared a workaround for Linux kernel and published a patch at the x86-64 mailing list.

Here is the description of the errata

https://www.x86-64.org/pipermail/dis...er/010259.html

This is the post including the patch

https://www.x86-64.org/pipermail/dis...er/010260.html

This part of the patch modifies the involved MSR registers to disable the TLB-fix if applied via bios.

MSR_K8_HWCR (Hardware configuration register) is the C0010015 register/* enable workaround for AMD Erratum 298 if necessary */

+ if ((c->x86 == 0x10) && (c->x86_model < 3) && (c->x86_mask != 3)) {

+ /* re-enable TLB caching if BIOS disabled it */

+ rdmsrl(MSR_K8_HWCR, value);

+ value &= ~(1UL << 3);

+ wrmsrl(MSR_K8_HWCR, value);

+ rdmsrl(0xC0011023, value);

+ value &= ~(1UL << 1);

+ wrmsrl(0xC0011023, value);

+ /* enable OS workaround */

+ e298_bug = 1;

+ printk(KERN_INFO "AMD erratum 298 workaround enabled\n");

+ }

What the code does is reading the two registers and setting exactly those bit's the #254 workaround recommends and write the values back to the registers.

After that it prints the message "AMD erratum 298 workaround enabled" to the kernel log.

The kernel log includes this line four times after startup so I assume it's applied to the MSR register of each core.

Note: A few users reported they had lookup's under heavy load whom here gone after they applied the kernel patch. They did not use virtualisation, so the errata is not an virtualisation only issue.

On Windows OSes there is no Hotfix available doing this workaround.

If you own a motherboard with an Bios which deactivates the TLB-Cache (TLB-Fix applied) and you can not use AOD to reenable it you can use one of the two following methods.

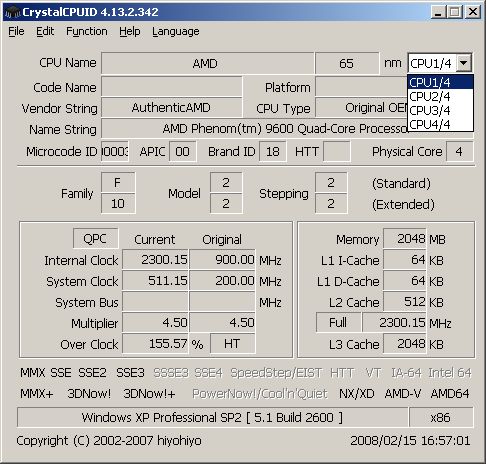

1. Manual way via CrsytalCPU.

Download and install CrystalCPU from here.

On the CrystalCPU's main Windows you can select the core with a dropdown in the upper right corner.

Apply the following steps to each core.

Select the Core in the main window.

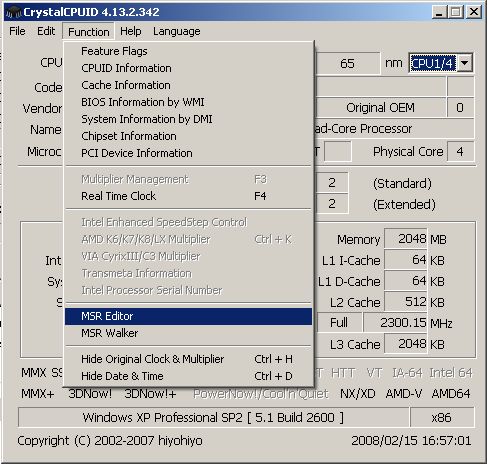

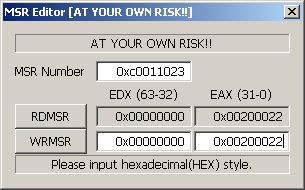

Start the MSR-Editor

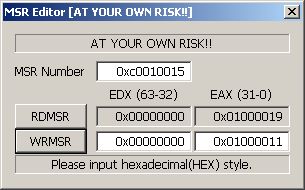

Enter C0010015 in the MSR Number field and hit RDMSR.

Change the last hex digit. Bit Nr. 3 (8h) must be unset. If the last digit is 8h use 0h if it's 9h use 1h. Hit WRMSR to apply the changes.

Now enter C0011023 in the MSR Number field and hit RDMSR.

Change the last hex digit. Bit Nr. 1 (2h) must be unset. If the last digit is 2h change it to 0h. Hit WRMSR to apply the changes.

Close the MSR Editor, select the next core start the MSR editor and change the registers the same way as described above.

2. Automated via a Script for RW-Everything

User mibo pointed to a much more convenient way to change the registers. Here is his Howto

wibo's updates script

Note: I recommend you check the actual values of your MSR registers and modify the script in case the last digit of register C0010015 is different from 8h or the last digit of register C0011023 is different from 2h. Some mobos have Bit Nr. 0 set in register C0010015.Code:>cpu 1 >rdmsr 0xc0010015 >LocalA = AND LocalA 0xfffffff7 >wrmsr 0xc0010015 LocalD LocalA >rdmsr 0xc0011023 >LocalA = AND LocalA 0xfffffffd >wrmsr 0xc0011023 LocalD LocalA >cpu 2 >rdmsr 0xc0010015 >LocalA = AND LocalA 0xfffffff7 >wrmsr 0xc0010015 LocalD LocalA >rdmsr 0xc0011023 >LocalA = AND LocalA 0xfffffffd >wrmsr 0xc0011023 LocalD LocalA >cpu 3 >rdmsr 0xc0010015 >LocalA = AND LocalA 0xfffffff7 >wrmsr 0xc0010015 LocalD LocalA >rdmsr 0xc0011023 >LocalA = AND LocalA 0xfffffffd >wrmsr 0xc0011023 LocalD LocalA >cpu 4 >rdmsr 0xc0010015 >LocalA = AND LocalA 0xfffffff7 >wrmsr 0xc0010015 LocalD LocalA >rdmsr 0xc0011023 >LocalA = AND LocalA 0xfffffffd >wrmsr 0xc0011023 LocalD LocalA >rwexit

3. Sam2008's Phenom TLB Disable Tool and Phenom MSR tweaking tool

Most convenient nowadays is this Tool

Read more ...

------------- old post ----------------

Hi,

Guess i found a way to disable the tlb fix if aod does not work and there is no option in the bios.

The latest bios for my M2A-VM included the tlb-fix. My everest memory read bandwidth dropped around 20%.

I expected bit nr 3 in the MSR register C0010015 to be responsible for the fix. So I compared the values between the two bios versions.

The old version showed 0x00000000 0x01000010 the new one 0x00000000 0x01000018 (bit nr 3 set).

The good thing one can use CrytalCPU's MSR Editor to disable the fix by changing that bit (...18->...10). At least it works on my board.

I could not enable the fix with the old bios by changing the bit. With the new bios i can turn it on and off on runtime.

Here are two screenies showing the MSR-Editor and the everest results.

TLB-Buffer enabled (no fix)

TLB-Buffer disabled (fix)

Description about what that bit controls from "AMD Family 10h Processor BKDG" p. 136

TlbCacheDis: cacheable memory disable. Read-write. 1=Disable performance improvement that assumes that the PML4, PDP, PDE and PTE entries are in cacheable memory. Operating systems that maintain page tables in uncacheable memory (UC memory type) must set the TlbCacheDis bit to insure proper operation.

Reply With Quote

Reply With Quote

Samsung LED 3D TV

Samsung LED 3D TV

Bookmarks