...I tried to find interestings registers in differents dumps

between fsb:398<->fsb:402,but a lot of registers change when

you apply this fsb values.So difficult to know what is good or no.

However,there are some common registers that change in this dumps

made by bachus_anonym and kunaak (965 chipset):

http://img239.imageshack.us/my.php?i...pbachusux2.jpg

http://img239.imageshack.us/my.php?i...pkunaakja9.jpg

For example register at offset 144 and 1F1...

but this register are "intel reserved" in datasheets,

and I don't know what they are.

I made a little soft that allow to edit the mchbar,

it's work on chipsets 865/875 and 9xx.

MemTweak.zip

It's run only in 32bits.

You can try to change these registers and other with this soft,

but warning,don't change anything,else it's possible crash...

Your first address must be (in left column) FED14000 for 9xx chipsets,and FECF0000 for 8xx.

Reply With Quote

Reply With Quote

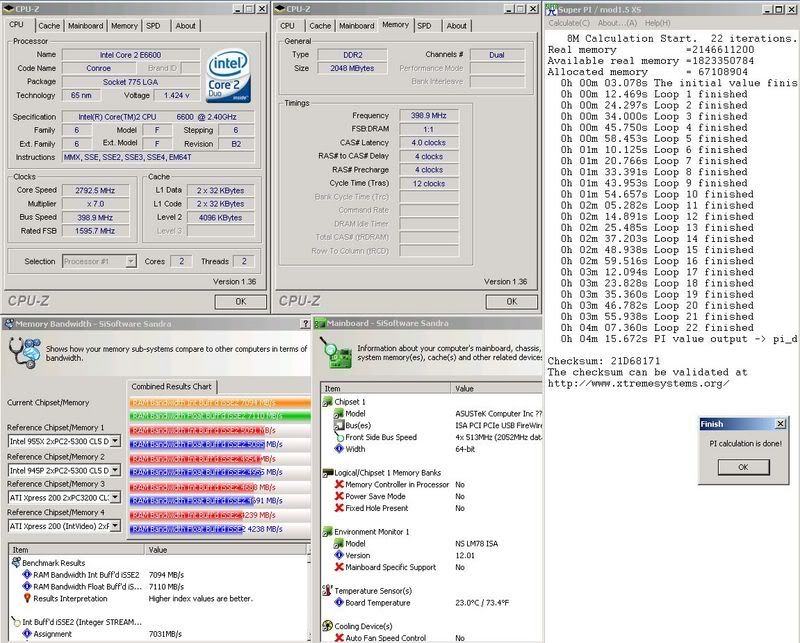

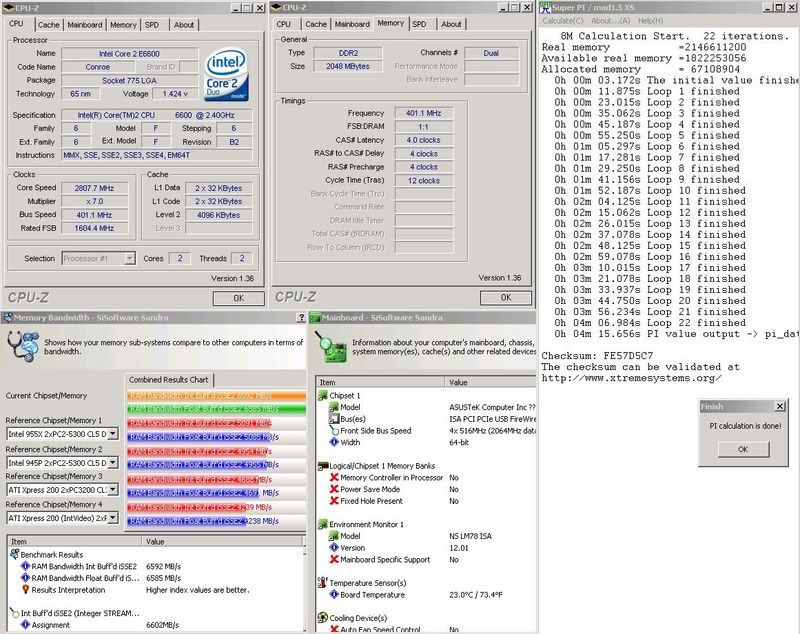

After that, I kind of stopped investigating it further, but I might try again, with more vmch. But yes, it is confirmed, just a matter of how high you manage to go. Just a note, this is no-go at any other ratio than 1:1

After that, I kind of stopped investigating it further, but I might try again, with more vmch. But yes, it is confirmed, just a matter of how high you manage to go. Just a note, this is no-go at any other ratio than 1:1

Bookmarks