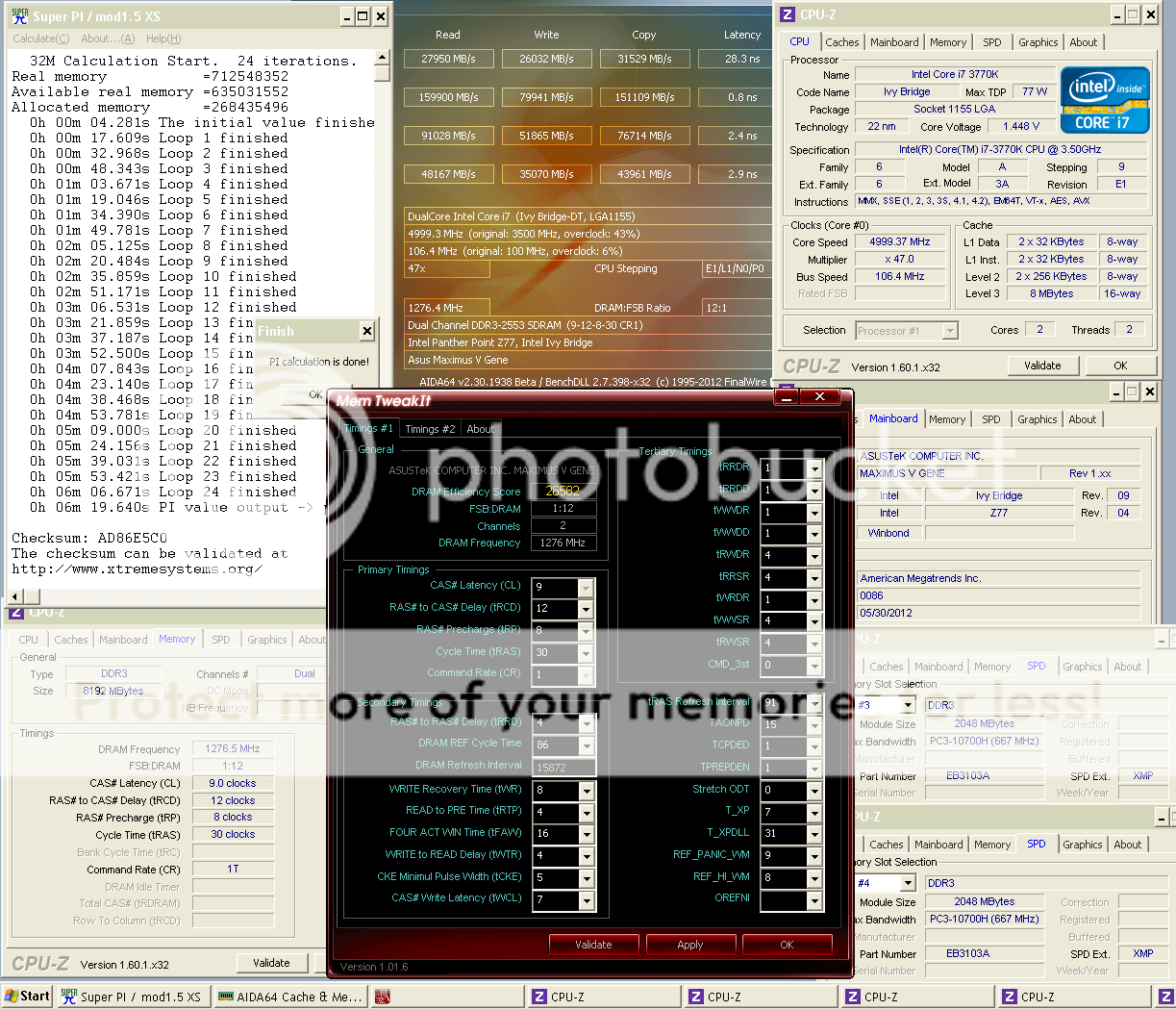

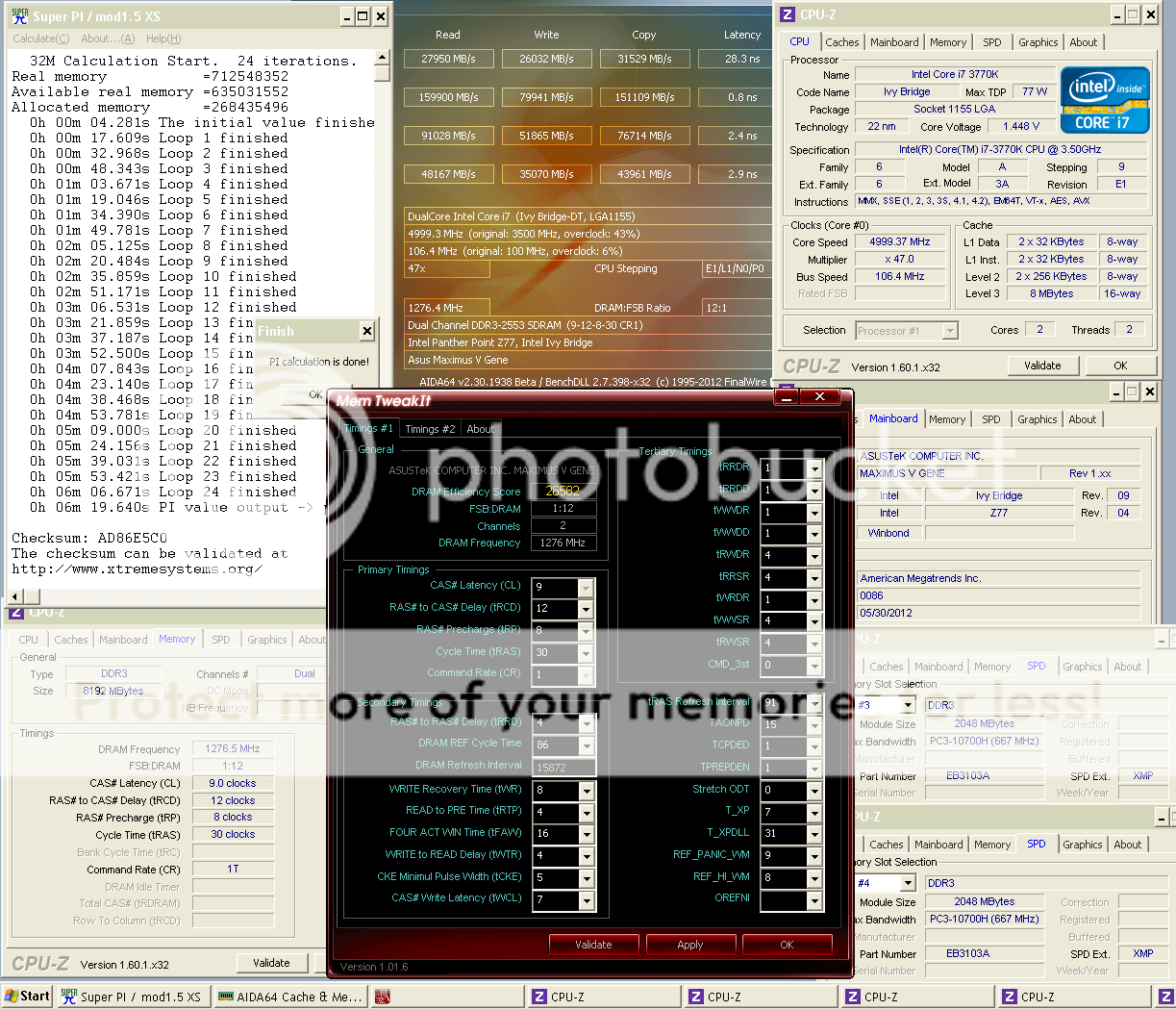

got up to 1276mhz but it only cut 0.14s from 1250mhz run. That includes using Spi Booster on 0086.

cheapseats - 6:19:640 - 48x106.4 - 1276.5MHz - 9-12-8-30-86-1 - ASUS MVG - Exceleram EB3103A 4x2GB/PSC - 1.85V - air

4x2GB

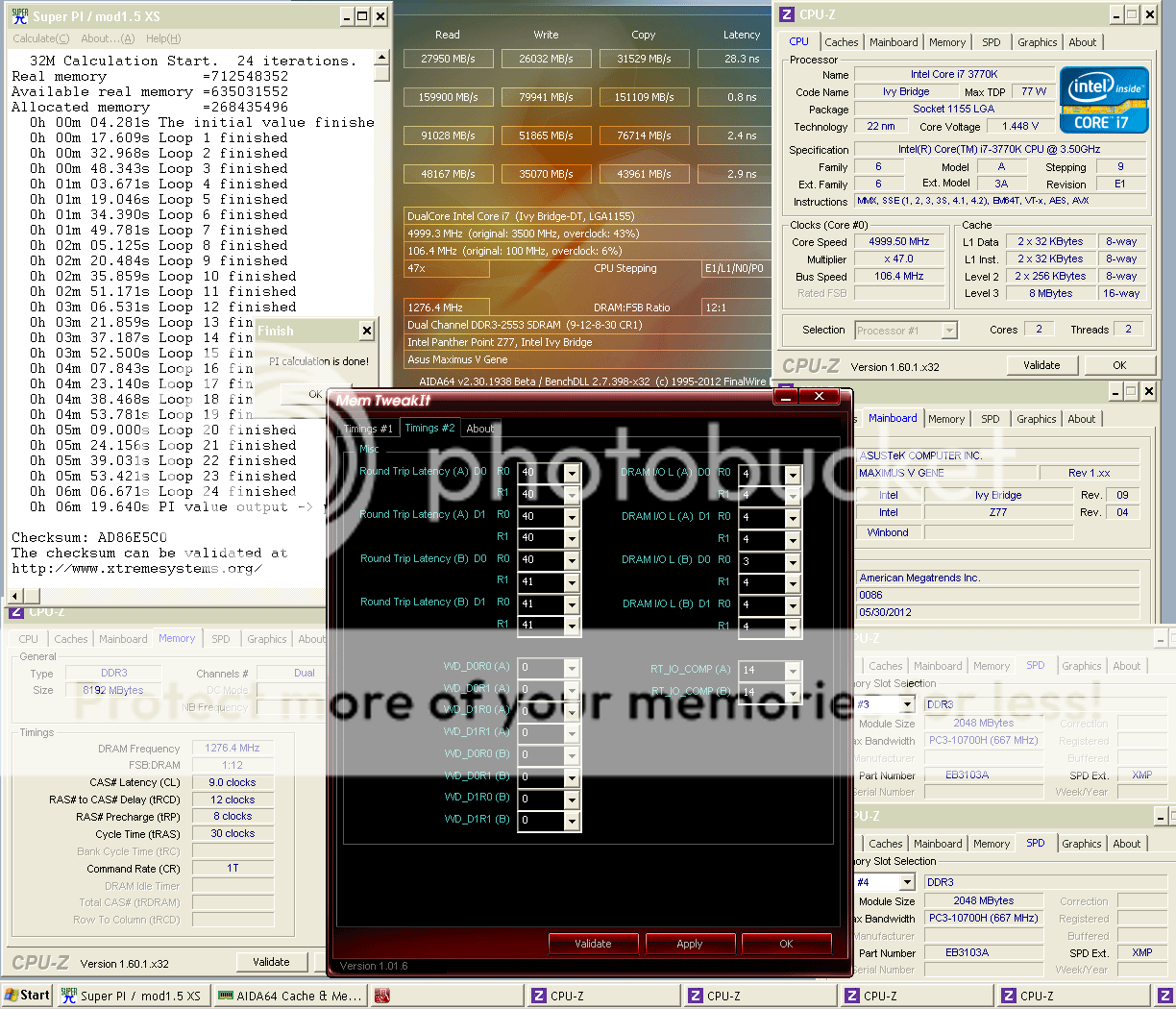

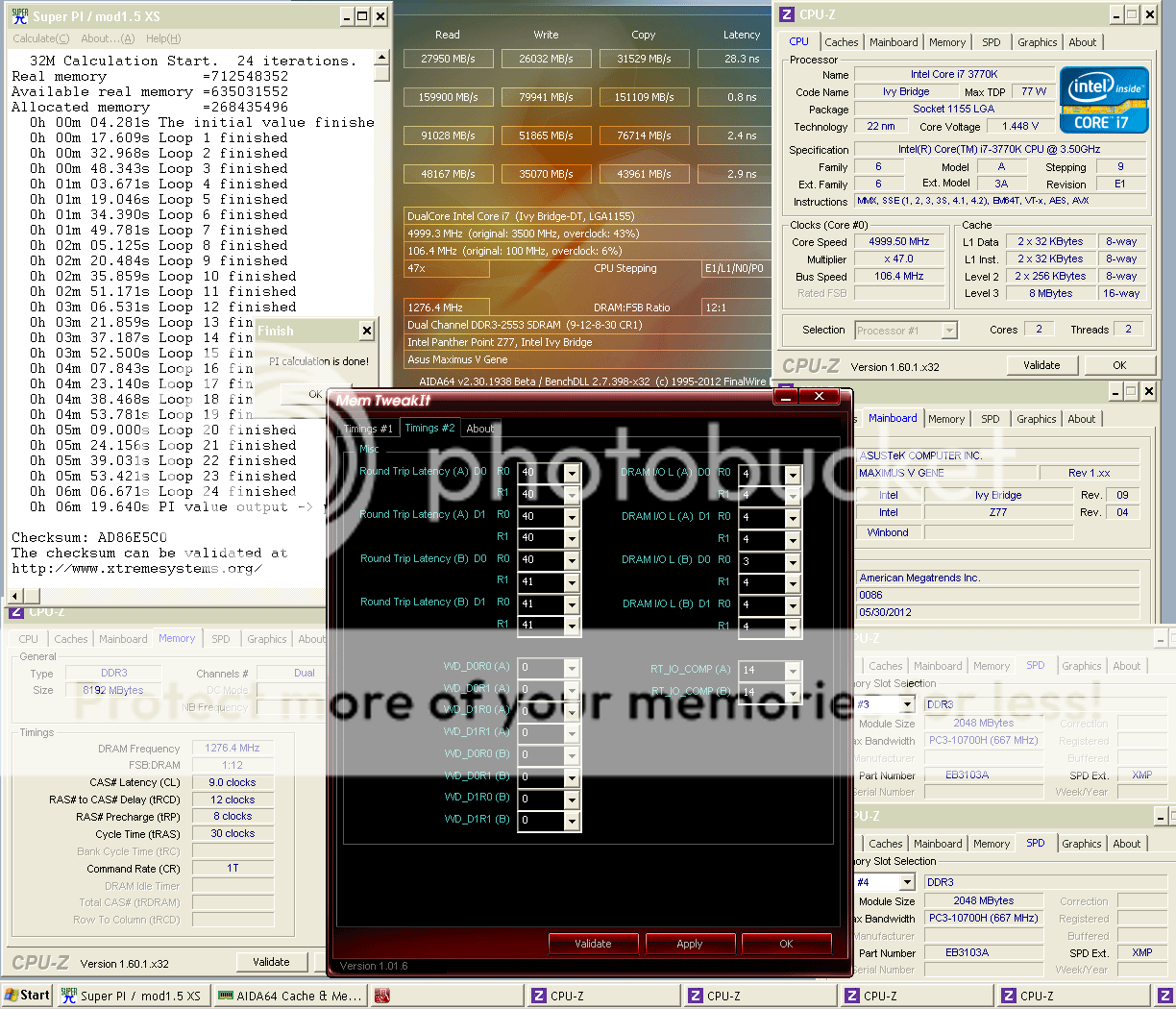

Memtweaker Timing#2

CHB DIMM 0 is tricky .. will only run with different RTL & IOL for ranks 0 & 1.

Sometimes boots with both ranks at 41 & 4 but fails at Loop 6. Only passes 32M if Rank 0 is 40 & 3

----------------------------

correct, CL values where WCL > CL is wasting time with PSC/BBSE.

this table was for Sandy + PSC, but the CL + WCL combinations for RTL & vDIMM scaling also apply to Ivy with PSC

the Hyper table was just a reference to show the differences in RTL scaling with PSC CL.

full thread and 32M tests:

CL|WCL|RTL performance (SB) : 32M scaling charts : PSC WCL > CL performance bug

Reply With Quote

Reply With Quote

Bookmarks