Well, I was rather board this w/e. So I decided to get creative with K10.5 Dies . My inspiration here was A. I don't fully agree with Han's prediction on the Istanbul die.. I don't think they'll re-arange cores or L3 Tags in reality. and B. The Die size "leaks" for Regor @ 80mm2 seem too small to me..

So If the nerdier members wish to give solid input on this feel free.. this is what i've come up with so far:

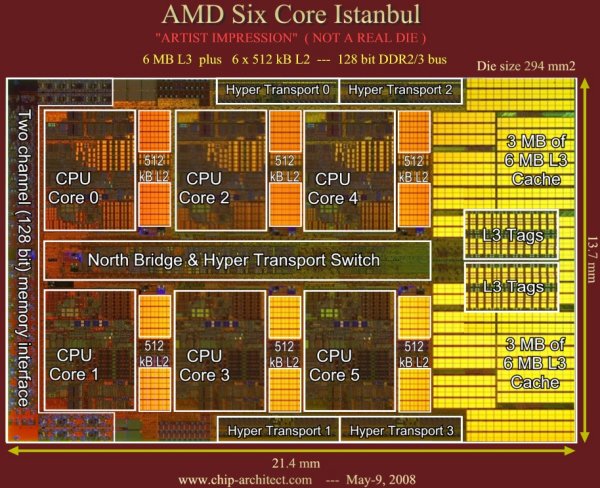

Istanbul: Hexa Core,6x0.5Mb L2 1x 6Mb L3

Main differences Vs Han's impression are:-

A. Maintaining core 1-4 layout.. I don't think AMD would really have the time or resource to rearange the existing cores, and hence all their datapaths in realtion to the NB.. personal thought, feel free to disagree.

B. I've moved HT link's to the side of the core as per Han's impression, but have only moved some L3 tiles to fill the space. I have a feeling the area between the two L3 Cache sections are buffers, and moving them would be a pain in the arse. Also, on shanghai there are 4 distinct logic 'blocks' in the NB. To me they're some sort of register/interface to the induvidual cores, so I've added 2 more of them for good measure.

I've also added some 'random' Logic to the "left" side of the centrally located Northbridge/bus logic section to account for Istanbuls new HT snooping feature.. I'm assuming the extra real estate afforded by adding the cores allowed them to add this technology. So i've snuck it in there. Feel free to suggest otherwise..

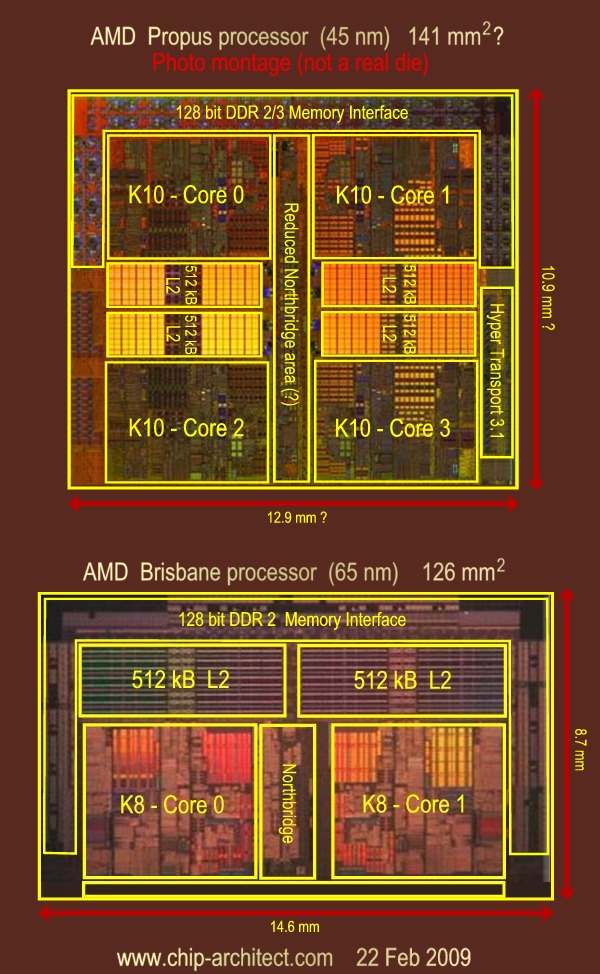

Regor: Dual Core 1Mb L2 x2

Here, I've essentially emulated the Griffin Layout with the exception of the single Full duplex HT link - I've copied K10's (not K10.5) method of running the HT link in 2 sections side by side behind the L2 (behind the L3 on K10).. reference the original K10 die for reference of what i'm talking about here. The extra space between cores I've used to widen the NB section. I've also removed 2 of the above mentioned NB sections from Shanghai/deneb, I feel they're related to each core so two wouldn't be needed. these are also the sections I moved to the sides to shorten and widen the NB section.

Anyway, as you can see I don't know how 80mm2 will be possible with these cores.. It seems the memory interface and HT Links DONT scale to well with process shrinks. They are Larger in scale with the core in comparison to 65nm. I also roughly tried combining the 2 "top" cores instead, but it still results in very similar ~100mm2 core size..

discuss!

Reply With Quote

Reply With Quote

) estimations that took Hans' Deneb and Istanbul illustrations into practice, Regor would have taken ~170mm^2. I'm rather sure the 141mm^2 number is really close to accurate. So they are slimming down something else than just the cHTT pads, too. What about memory and the HT switch? Could be more optimized for space?

) estimations that took Hans' Deneb and Istanbul illustrations into practice, Regor would have taken ~170mm^2. I'm rather sure the 141mm^2 number is really close to accurate. So they are slimming down something else than just the cHTT pads, too. What about memory and the HT switch? Could be more optimized for space?

Samsung LED 3D TV

Samsung LED 3D TV

Bookmarks