Stock or close to it. Very low HT, to try and eliminate any variables apart form clock speed.

Yeah unfortunately my chip is not like yours, its worse. Either that or the board/BIOS is bad, but I don't think its the latter for some reason, maybe I should now test another 790FX board and see. Not load stable, load stable it can easily do 1.48v ID / 1.440v LD 3055MHz - but the idling stability which has plagued us.With an 14,5 cpu multi a 10x nb multi is very unstable here. An 11x multi is alot more stable but needs ~0.05V more than with an 14x cpu multi.

Anyway 2.9/2.2 works fine here with 1.4V/1.35V only limit are the temps here. They must have reached 85°C here because thats where the board powers off and the system was of this morning. During the firs 15 minutes or so the cpu temps where in the 70°C area.Temps are good with this cooler, TT120 and Zalman 9700 could not handle this heatload even for 3 minutes under load.

I am thinking of picking up your board again... MSI is just not letting out a BIOS I can use to oc properly and I've ran out of time for computing this year - which BIOS are you using and do you recommend? Is there a large vDroop and vDrop on the board?

It'll most likely be like the Team Group kit, 2.45v 6-6-6-18 1300 - I hope not, but I have a feeling it will be.DDR2-1300 kit sounds promising.

Good to know, at least there's no CB upto -40C

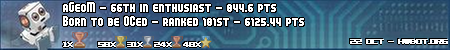

I'm currently testing the below setting: 1.516v ID / 1.480v LD 2914MHz. Load is stable, idling stability so far is OK, more than 80mins into it but need to let it run at least a day or two to see if it fails.

Tried 2940 at the same voltage before, it failed after Crysis for about 30 mins, back to desktop, nothing open, idling, it froze.

I'll test NB/HT/HT Link/RAM max and stability later. I'm not looking forward to it though.

Reply With Quote

Reply With Quote

Is that normal? I was using the 9500.

Is that normal? I was using the 9500.

Bookmarks