Hmmmm, I thought you said black PCB & spreaders

I've been through a few sets of sticks lately... probably be through a few more over the next little while...

Once I get my QX9650 I'll be looking for a set that can play nice with that and my MaxFor...then I'll have to stop for a while (if I want to stay married).

I should have kept the ReaperX 4GB set I had that was stable at 5-5-5-12 @ 1066 with Strong Twister/Static Read Enabled/Trans Booster enabled (0)

RIG 1 (in progress):

Core i7 920 @ 3GHz 1.17v (WIP) / EVGA X58 Classified 3X SLI / Crucial D9JNL 3x2GB @ 1430 7-7-7-20 1T 1.65v

Corsair HX1000 / EVGA GTX 295 SLI / X-FI Titanium FATAL1TY Pro / Samsung SyncMaster 245b 24" / MM H2GO

2x X25-M 80GB (RAID0) + Caviar 500 GB / Windows 7 Ultimate x64 RC1 Build 7100

RIG 2:

E4500 @ 3.0 / Asus P5Q / 4x1 GB DDR2-667

CoolerMaster Extreme Power / BFG 9800 GT OC / LG 22"

Antec Ninehundred / Onboard Sound / TRUE / Vista 32

i have the F2-8000CL5D-4GBPQ kit and they run perfectly stable @ 1086 or 1088 (whichever speed it hits) 5-5-5-12. it takes 2.2vdimm though.

Can you set twister strong on strap 333/5:6 divider or only this is the only combination '5-5-5-12 @ 1066 with Strong Twister/Static Read Enabled/Trans Booster enabled (0)' ?

E8400 TRUE120@Asus Maximus Formula@2x2GB Geil Evo One 800MHz 4-4-4@Corsair HX 620W

Sapphire HD6850 1GB@Samsung 830 128GB@Casetek 1022-5@LG 19" 1970HQ

Creative Inspire 5.1 5100@Samsung SH-S203B SA@CM Quickfire Pro Red@Logitech G-600

Can someone please help or explain why after the boot screen I get the error messege "cpu over voltage error!, F1 to continue". It only happens when I put the voltage up to 1.62 or higher. Anything below that this messege doesn't come up.

The board has been great since I got it release week. Temps aren't an issue. NB/SB under 39, CPU cores 1-4 idle 30-35, OCCT load 60-64 across.

I use the tweak guides here and on AnAndTech for bios settings. At 3.82 on the Q6600 G0, and 3870x2 @850 core, 900 memory I get 19,337 3dMark06. Crysis and BF2 run great on my Samsung 1680x1050 2ms.

TRAS 12 will not gain you anything with the larger density, you have to remember you are not setting the max the controller will use, you are setting the minimum...this means most of the time the lower value will not be used BUT if it is and the pages are closed to fast you will force the ram to re-read. Its always best to tune TRAS and set the highest value that gives you the highest bandwidth.I should have kept the ReaperX 4GB set I had that was stable at 5-5-5-12 @ 1066 with Strong Twister/Static Read Enabled/Trans Booster enabled (0)

so what im saying is 12 is to tight, unless you play superpi all the time you are forcing rereads and losing performance.

Got a problem with your OCZ product....?

Have a look over here

Tony AKA BigToe

Tuning PC's for speed...Run whats fast, not what you think is fast

CPU Q6600 G0 @3.6 1.34v

Ram 4x1024 Crucial Ballistix Tracer DDR2 @5-5-5-15 1066mhz 2.12v

Graphics EVGA GTX280 1GB @stock

Displays 24" Westinghouse L2410NM| 19" Dell 1907FP

Storage 4 x 500G WD5000AAKS RAID10

Mobo Asus Maximus Formula X38 (Rampage Mod 0701)

Case Kandalf VD4000 LCS black

PS Ultra X2 750W

OS Windows Vista x64 SP2

Sound Supreme FXII 8.1 | Audio FX Pro 5.1 Headset

Media Liteon DH20A3H External 20x DVD+/- DL

Cooling Tt P500 pump | 3/8 green tube | Tt 350cc Res | Tt 360mm radiator w/ 3 120mm Tt silent fans | Swiftech MCW30 NB | Tt 208 copper CPU

RIG 1 (in progress):

Core i7 920 @ 3GHz 1.17v (WIP) / EVGA X58 Classified 3X SLI / Crucial D9JNL 3x2GB @ 1430 7-7-7-20 1T 1.65v

Corsair HX1000 / EVGA GTX 295 SLI / X-FI Titanium FATAL1TY Pro / Samsung SyncMaster 245b 24" / MM H2GO

2x X25-M 80GB (RAID0) + Caviar 500 GB / Windows 7 Ultimate x64 RC1 Build 7100

RIG 2:

E4500 @ 3.0 / Asus P5Q / 4x1 GB DDR2-667

CoolerMaster Extreme Power / BFG 9800 GT OC / LG 22"

Antec Ninehundred / Onboard Sound / TRUE / Vista 32

Hardware monitoring in the bios. set CPU voltage to "ignore"

Also, does anyone have any suggestions on how to get 2x 2gb OCZ Platinum 8000 to run at 1066 on this board? I was getting it to boot in 0504 then updated to 1003 and nothing. I know it has to do with performance level and sub timings but i can't figure it out.

Last edited by iadstudio; 02-27-2008 at 03:15 PM.

They old Fool is still looking for a 24/7 setting (incl. second ram kit to be added).

Intel's sample still doing fine. Ram is selected D9GMH. 3 SPD's programmed by vendor. Ref. sig.

Any hints and tips welcome.

Kind regards

The Fool

NH-U12F(NF-P12)/QX6850/Maximus Formula/2x Cellshock CS2221550

HD5870 VaporX/SB X-Fi Fatal1ty/WD1500HLFS stripe/WD6401AALS/iHAS424

Enermax Modu 87+ 600W/Lian Li A16A/aquaero 4.0 VF

test and see, and don't run pi as that is the only THING that likes tighter TRAS, run actual games and do some photo editing or encoding...something real.

test TRAS with memtest...note the bandwidth as you test each value and set the highest value that gives the best bandwidth, so if 5,6,7,8,9,10,>>>>18 all give 5000MB/s and 19 gives 4890 set 18

Its like tRFC, if the rows are refreshed to fast they may force the minimum setting for TRAS to be used, so if you have tRFC to tight and TRAS set to say 8 you may have a situation with rows closing to fast and TRAS forcing rereads...so you lose performance.

128x8 ram IC's are massive density, 8GB has lots of load and lots of rows, running these modules like a 1GB micron D9 module is not going to cut it no more....you have to set what works...not what you think is fast

imagine what 256x8's are going to be like as DDR3 scales up

The one thing I have noted from the IC's we and a few others are using for the 4GB kits is they will do 1000 or so dead easy at 1.8V, many do 950ish at 1.7V but as soon as you move over the sweet spot to say 1050+ you have to ramp the juice to 2 then 2.1 very quickly.

It pays to really fine tune this stuff to keep everything stable and as unstressed as you can.

Got a problem with your OCZ product....?

Have a look over here

Tony AKA BigToe

Tuning PC's for speed...Run whats fast, not what you think is fast

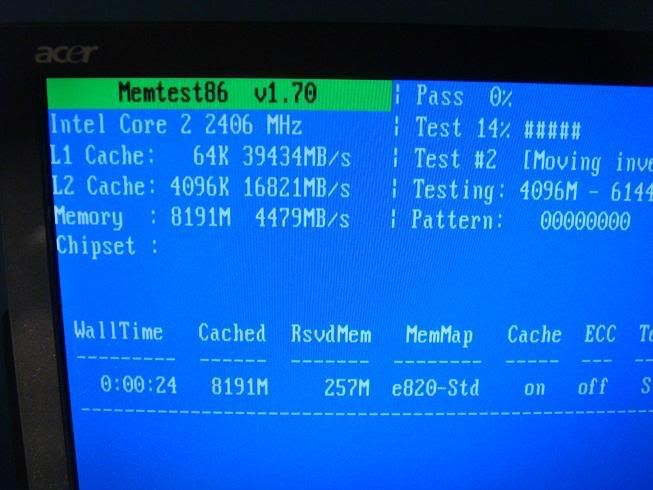

I've run with mine on Disabled for the longest time, since I got the Board. Tested 440-456 FSB with Enabled and Disabled and it seemed to do little for stability, seems more a performance related setting? I didn't boot into XP, I was just testing using Memtest Test 5.DRAM Static Read Control:

This function is best set to "Disabled" for high FSB levels (450 FSB upwards). "Enabled" gives a small gain in memory access latency at the expense of overall stability. We believe this setting alters a single TRD phase to low; performance advantages either way are not stellar.

Last edited by zlojack; 02-27-2008 at 06:32 PM.

RIG 1 (in progress):

Core i7 920 @ 3GHz 1.17v (WIP) / EVGA X58 Classified 3X SLI / Crucial D9JNL 3x2GB @ 1430 7-7-7-20 1T 1.65v

Corsair HX1000 / EVGA GTX 295 SLI / X-FI Titanium FATAL1TY Pro / Samsung SyncMaster 245b 24" / MM H2GO

2x X25-M 80GB (RAID0) + Caviar 500 GB / Windows 7 Ultimate x64 RC1 Build 7100

RIG 2:

E4500 @ 3.0 / Asus P5Q / 4x1 GB DDR2-667

CoolerMaster Extreme Power / BFG 9800 GT OC / LG 22"

Antec Ninehundred / Onboard Sound / TRUE / Vista 32

I just finished testing memtest with 4x 2GB OCZ Reapers @ 4-4-4-15 with 2.1v. Everything seems to be working fine, can't wait to plop in my Q6600 and see how it goes.

Will I need improved NB cooling for 1600 FSB?

Work in progress ...

Core2 Q6600 @ 3.6GHz | Asus Maximus Formula

4x 2GB OCZ Reaper | 1x 74GB WD Raptor | 2x 250GB Seagate

EVGA ACS3 8800 GTX | 1000w Ultra X3 | Thermaltake Armor LCS | Swiftech Apogee GT

RIG 1 (in progress):

Core i7 920 @ 3GHz 1.17v (WIP) / EVGA X58 Classified 3X SLI / Crucial D9JNL 3x2GB @ 1430 7-7-7-20 1T 1.65v

Corsair HX1000 / EVGA GTX 295 SLI / X-FI Titanium FATAL1TY Pro / Samsung SyncMaster 245b 24" / MM H2GO

2x X25-M 80GB (RAID0) + Caviar 500 GB / Windows 7 Ultimate x64 RC1 Build 7100

RIG 2:

E4500 @ 3.0 / Asus P5Q / 4x1 GB DDR2-667

CoolerMaster Extreme Power / BFG 9800 GT OC / LG 22"

Antec Ninehundred / Onboard Sound / TRUE / Vista 32

Big Garoupa, what kind of cooler is that???

Main system:

Q6600 G0 L737B 3,8GHz

Maximus Formula X38

Ballistix PC2-8500 2x1GB

XFX 8800GT XT

Corsair HX620

X-Fi Platinum

150GB Raptor (Dual Boot) /2x 250GB WD Caviar (Apps)

Lian-Li V2000B Plus II

School: MacBook

Studying in: Pharmacy

Where: University of Montreal

Did you notice any "improvments" in the way the NB contacts/grease were installed?

Edit: Nevermind you can see the Revision in this pic. I'm pretty sure it says 1.03G

Ok thanks for your input, I went with the 4gb G.Skill 1000 kit. I hope they arrive soon enough. Jeez, i can't wait. The Asus BIOS said, my q6600 is a 1.25 or (something like that) VID, i'm starting to wonder if i got lucky..

Run Coretemp to discover ya VID not the bios... eg my QX9650 is a 1.125Vid though Asus bios sets 1.2volts while it only needs 1.1 to be stable at stock speeds...

Question : Why do some overclockers switch into d*ckmode when money is involved

Remark : They call me Pro AsusSaaya yupp, I agree

Got a problem with your OCZ product....?

Have a look over here

Tony AKA BigToe

Tuning PC's for speed...Run whats fast, not what you think is fast

Opinions...

Should I stick with my Ballisitix Tracer PC6400 4 x 1024MB

or...

go with OCZ Gold edition PC6400 4 x 2048MB

I have both sets now but what should run better? Are the platinum much better or any at all vs the gold edition OCZ Tony ?

CPU Q6600 G0 @3.6 1.34v

Ram 4x1024 Crucial Ballistix Tracer DDR2 @5-5-5-15 1066mhz 2.12v

Graphics EVGA GTX280 1GB @stock

Displays 24" Westinghouse L2410NM| 19" Dell 1907FP

Storage 4 x 500G WD5000AAKS RAID10

Mobo Asus Maximus Formula X38 (Rampage Mod 0701)

Case Kandalf VD4000 LCS black

PS Ultra X2 750W

OS Windows Vista x64 SP2

Sound Supreme FXII 8.1 | Audio FX Pro 5.1 Headset

Media Liteon DH20A3H External 20x DVD+/- DL

Cooling Tt P500 pump | 3/8 green tube | Tt 350cc Res | Tt 360mm radiator w/ 3 120mm Tt silent fans | Swiftech MCW30 NB | Tt 208 copper CPU

test and see what they will do, remember you are tRFC limited on this board unless you run 1001 or 1003 bios or earlier.

Got a problem with your OCZ product....?

Have a look over here

Tony AKA BigToe

Tuning PC's for speed...Run whats fast, not what you think is fast

Bookmarks