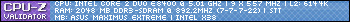

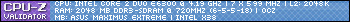

Gigabyte 965 board.

all voltage max.

Corsair 5400 UL V1.2.

cas 3-1-1-9.

I have bandwidth shots from all latencies down from 3339 to 3119 to make sure each latency was actually doing something, and while the differnce isn't drastic in any case, every setting did effect the bandwidth...

TRP 1 I can see as possible.

but Ras to Cas 1... thats some huge thing to expect from ram, so I find it almost crazy to think this might be possible.

I can test this in any way anyone wants to...

right now I am running Super Pi 1.5XS on it, at 3.5 ghz, with a old prescott 560.

in case anyone wants to say its reporting the wrong cas... heres how to fix that.

Bios F3. use the red slots. set your ram to the 2.66 multiplier.

thats the best way I found for the bios to report the correct latency.

still cannot set ras to cas 2 or TRP 2 within bios and have it stick, it just defaults to ras to cas 3 and TRP3.

settings were changed with Memset965.

bandwidth is low, cause I was still using version 2006 which reports about 1000 mbs lower then version 2007.

super PI 32M, appears to be half done, and stable cas 3-1-1-9.

will do cas 3-3-3-9 next to make sure, somethings actually different.

Reply With Quote

Reply With Quote![Send a message via AIM to [XC] moddolicous](images/misc/im_aim.gif)

or this

or this

Or it's that Memset that lets you pick-n-choose whatever you want and even apply it

Or it's that Memset that lets you pick-n-choose whatever you want and even apply it

Bookmarks