At low speeds yes. At 2.8 and 3Ghz its already 125W TDP again. The new limit just moved abit upwards. But it behaves just as with 65nm. Try a lower clocked 65nm Phenom/Barcelona and you see alot lower power consumption.

To compare you can buy 3.4 and 3.5Ghz 45nm Xeons.

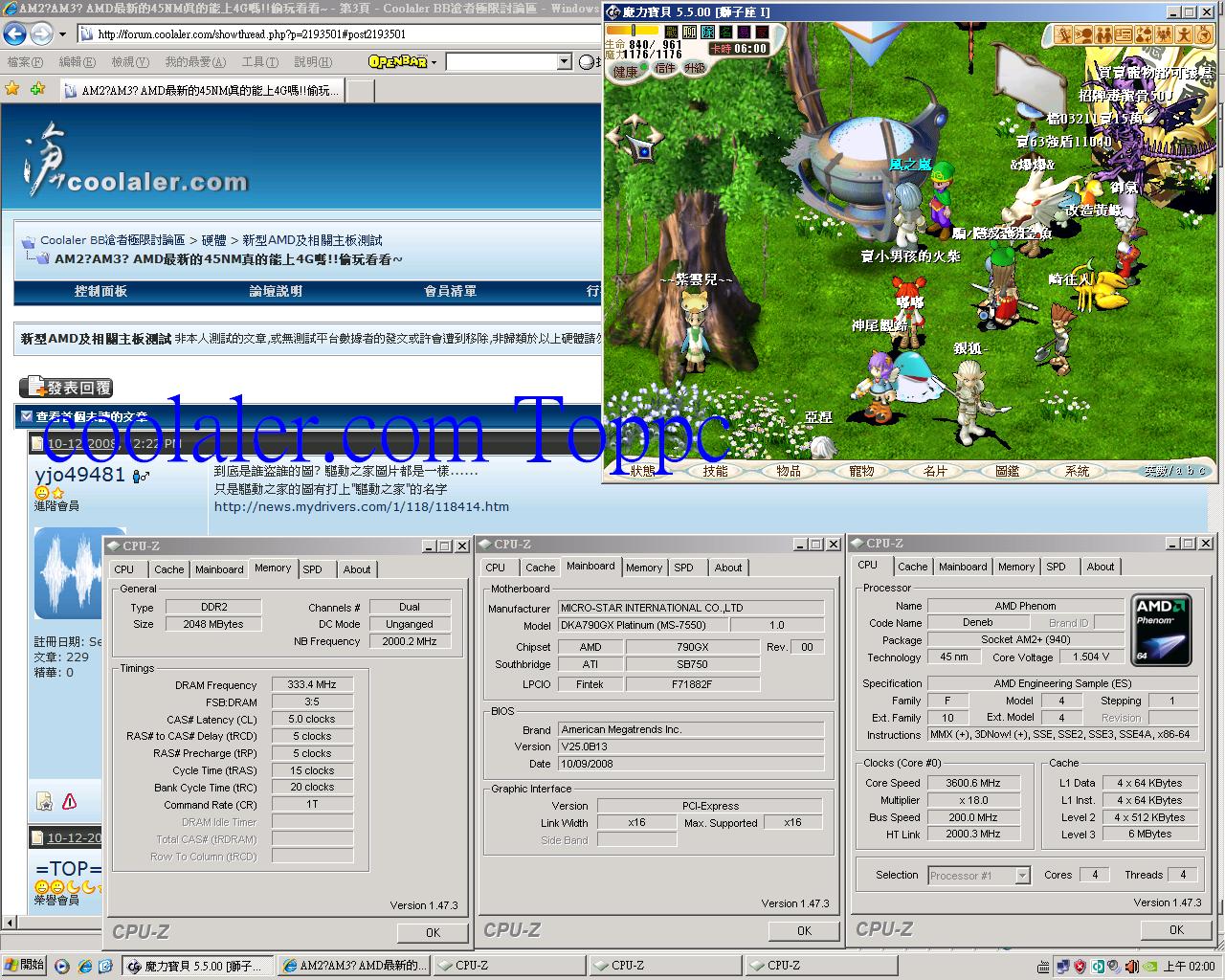

1.5V Deneb C1 3.6G Stable air. Deneb C1 uses 1.368V for 3Ghz

And 1.6V for 3.8Ghz.

Reply With Quote

Reply With Quote

Bookmarks