Yeap would be nice to have CodeRed back on here

Yeap would be nice to have CodeRed back on here

i5 750 4.20GHz @ NH-D14 | 8GB | P7P55DLE | 8800U | Indilinx SSD + Samsung F3 | HAF922 + CM750W

Past: Q6600 @ 3.60 E6400 @ 3.60 | E6300 @ 3.40 | O165 @ 2.90 | X2 4400+ @ 2.80 | X2 3800+ @ 2.70 | VE 3200+ @ 2.80 | WI 3200+ @ 2.75 | WI 3000+ no IHS @ 2.72 | TBB 1700+ @ 2.60 | XP-M 2500+ @ 2.63 | NC 2800+ @ 2.40 | AB 1.60GHz @ 2.60Originally Posted by CompGeek

Hi all

Great tweaker code red! Its been a life saver for me as I cant set 1T ram timing in the bios on my K8N neo 2

Was just trying your 0.5 beta and the Link Frequancy ( HTT Multi) seems to work fine on my neo 2 both cbid and sisoft sandra detect the front side bus changes.

In your last post you mentioned htt options not working so is it changing or not is what im wondering?

Regards and hope you continue making this great app.

Hi tictac.

1.)

This:

http://xtremesystems.org/forums/showthread.php?t=56354

also may interests you.

BNOBTC v6 with totally new version of:

AMIBCP

ModBin6 (2.01.01 (06/25) 2003)

CBROM (CBROM32 1.33, 1.41, 1.44)

Flash utilities etc.

will be released soon.

http://bnobtc.pix-art.com

2.)

Code:header: 55 AA ; Boot Able rom jmp init ; jump to code intialization retf ; return far to system bios file INIT pushad push eax push edx mov eax,0x80002184; eax=Bus0Dev2Func1,Offset 84,85,86,87 mov dx,0cf8 ; set dx as adress port out dx,eax ; send the address to IO Space throgh dx port mov dx,0cfc ; set dx as data port in eax,dx ;Receive the data into eax for the address we sent through dx port and eax,XXXXXX ; Change the data or eax,XXXXXX ; Change the data out eax,dx ; Send back the modded data through dx port pop edx, pop eax popad ret ; return to header last bit; use 8 bit checksum

The assembler code looks really interesting and this idea is similar to the ROMOS project.

http://hosting.modflex.com/rayer/romos/romose.htm

ROMOS booting in Bochs PC Emulator

ROMOS booting in VMware

(Weird chars appeared while booting ROMOS in VMware,

but there was no reason for this.

New releases of VMware may do not have this bug anymore.)

(PNG conversion and highest possible lossless PNG optimization & file size reduction by:

Borg Number One - borg_no [dot] one -at- gmx [dot] net

Thanks go to GIMP, PNGCRUSH and PNGOUT)

Well, I just would like to know what values have I to replace with xxxxxx?

Last edited by Borg Number One; 05-18-2005 at 10:25 AM.

BNOBTC & BNOBLG

Borg Number One's:

- BIOS Tool collection

- BIOS modifications

- BIOS Logo gallery

███████████████████████████████████████

http://bnobtc.pix-art.com

███████████████████████████████████████

where is the link to the lastest a64 tweaker? is it the 0.31 ver on page 1?

Bump!

I'd like to know the same thing. Where can I download 0.6 beta, the one I see everyone else using?

EDIT: Nevermind, I guess a bit of thread searching does the trick. Here's the post with all the download links for all you other lazy people: http://xtremesystems.org/forums/show...532#post711532

7700k @ 5.0GHz

ASUS Z170-Deluxe

2x8GB Avexir Raiden DDR4-3000 15-15-15-35

Gigabyte Aorus 1080 Ti @ 2076/1500(6000)

512GB Samsung PM961 + 840 Pro 256GB + some TBs

Corsair AX1200i

X-Star DP2710LED @ 110Hz + 40" Samsung TV

CPU and GPU under water: 9x120 rad + 3x120 + 3x120

...and an HTC Vive!

thought this was a new 0.6 beta but apparently not :P

anyway just thought that i'd mention that 0.6b and 0.51xt both had the same bug on my machine

if i save the current settings and load them again they arent the same :/

max bypass is changed to 0x and tref is changed to 100mhz 15.6µs

Borg Number One... have you seen with pinczakko source code..

he hack down realtek NIC rom

Code:;-------------------------------------------------------------------; ;The base code created in 2:34 am May 4th 2003 ;Successfully patched in 9:35 am July 28th 2003 ;by Darmawan MS a.k.a Pinczakko. ; ;This is my first operating system prototype :). One thing still ;obscured, the BEV mechanism mentioned in Plug & Play BIOS spec 1.0A ;don't explain about how the code executed :(. But based on my ;experiment it seems to be executed from ROM. So everything we do ;prior to loading the OS code from the expansion ROM into the RAM ;can't do anything dealing with memory write operation. I think ;BEV works as follows : ;1. During POST, the main bios recognize the LAN card as boot device. ;2. If we set up the main bios to boot from LAN as default, after POST succeded, ; int 19h (bootstrap) will point into the PnP option rom BEV of the LAN ; and passes execution into the code there, so we're executing code ; in the ROM pointed to by the BEV. Unless we're loading part of this ; code into RAM and execute from there, there's no writeable area in our code ; ;While the PCI function of the LAN card function as ordinary PCI card does ;so, the PCI init function has no direct connection with the BEV related stuff. ; ; <--------- HACK IT DOWN D00D -----------> ; ;--------------------------------------------------------------------; [BITS 16] ;Real mode by default (prefix 66 or 67 to 32 bits instructions) [ORG 0x00] ;-------------------------------------------; ; Option rom header ;-------------------------------------------; db 0x55 ;;Rom signature byte 1 db 0xAA ;;Rom signature byte 2 ROMsize db ROM_Size ;;1024 bytes jmp INIT ;;jump to initialization Times 0x18-($-$$) db 0 ;;zero fill in between dw PCI_DATA_STRUC ;;Pointer to PCI HDR structure (at 18h) Times 0x1A-($-$$) db 0 ;;zero fill in between dw PnP_Header ;;PnP Expansion Header Pointer (at 1Ah) ;---------------------------- ; PCI data structure ;---------------------------- PCI_DATA_STRUC: db 'PCIR' ;PCI Header Sign dw 0x9004 ;Vendor ID dw 0x8178 ;Device ID dw 0x00 ;VPD dw 0x18 ;PCI data struc length (byte) db 0x00 ;PCI Data struct Rev db 0x02 ;Base class code, 02h == Network Controller db 0x00 ;Sub class code = 00h and interface = 00h -->Ethernet Controller db 0x00 ;Interface code, see PCI Rev2.2 Spec Appendix D dw ROM_Size ;Image length in mul of 512 byte, little endian format dw 0x00 ;rev level db 0x00 ;Code type = x86 db 0x80 ;last image indicator dw 0x00 ;reserved ;----------------------------- ; PnP ROM Bios Header ;----------------------------- PnP_Header: db '$PnP' ;PnP Rom header sign db 0x01 ;Structure Revision db 0x02 ;Header structure Length in mul of 16 bytes dw 0x00 ;Offset to next header (00 if none) db 0x00 ;reserved db 0x7A ;8 Bit checksum (for this header, --> ; --> check again after compile and repair if needed) dd 0x00 ;PnP Device ID --> 0h in Realtek RPL ROM dw Manufacturer_str ;pointer to manufacturer string dw Product_str ;pointer to product string db 0x02,0x00,0x00 ;Device Type code 3 byte db 0x14 ;Device Indicator, 14h from RPL ROM-->See Page 18 of ;PnP BIOS spec., Lo nibble (4) means IPL device dw 0x00 ;Boot Connection Vector, 00h = disabled dw 0x00 ;Disconnect Vector, 00h = disabled dw Start_OS ;Bootstrap Entry Vector (BEV) dw 0x00 ;reserved dw 0x00 ;Static resource Information vector (0000h if unused) ;---------------------------------------------------------- ; Identifier strings ;---------------------------------------------------------- Manufacturer_str db 'Pinczakko Corporation',00h Product_str db 'Realtek Hacked ROM',00h ;-------------------------------------------------------------------- ;PCI Option ROM initialization Code (init function) ;-------------------------------------------------------------------- INIT: lea si,[msg] ;fetch the string addr call dis_string ;display the message mov bx,ROMsize ;clean up memory used (set image size to 0) xor ax,ax ;produce 0000h mov [bx],ax ;3rd byte of this bios image file (image size) or ax,0x20 ;inform system BIOS that an IPL device attached ;see PnP spec 1.0A p21 for info's retf ;return far to system BIOS msg db 10,13,'PCI expansion rom initialization called...','$' ;-------------------------------------------------------------- ; -- Procedure to display string to stdout -- ;Procedure definition:displaying character done through ;int 10h,service 0Eh ;-------------------------------------------------------------- dis_string: cld .more_dis: ;display OS message lodsb cmp al,'$' je .no_more_dis mov ah,0xE mov bx,0x7 int 10h jmp .more_dis .no_more_dis: retn ;-------------------------------------------------------------------- ; Operating system entry point/BEV implementation (BootStrap) ;-------------------------------------------------------------------- Start_OS: mov ax,cs mov es,ax ;make all segment reg to --> mov ds,ax ;point to the right segment lea si,[msg_PnP] ;fetch the string addr call dis_string ;display the message mov ah, 0x00 int 0x16 ;wait for key to be hit ;---------------------------------------------------------------------------------- ;--- Load The Operating System Code beginning at OS_Load_Seg :OS_Load_Offset h ---- ;---------------------------------------------------------------------------------- cli ;disable interrupt during loading mov ax,OS_Load_Seg ;point to OS segment mov es,ax mov ax,OS_Load_Offset ;point to OS offset mov di,ax lea si,[OS_Code] ;equal to lea si,OS_Code in masm cld xor ecx,ecx mov ecx,OS_Code_Size16 load_os: lodsw stosw loop load_os ;-------- Loading completed ------------------------------------- mov ax,cs ;restore es segment register mov es,ax xor di,di jmp OS_Load_Seg:OS_Load_Offset msg_PnP db 10,13,'PnP BEV Routine Invoked!',10,13,'$' ;------------------- WARNING !!! ----------------------------------; ;-- The linear address here must match the second file (OS code) --; OS_Load_Seg equ 0x7C0 OS_Load_Offset equ 0x0000 ROM_Size equ 0x04 ;ROM size in multiple of 512 bytes OS_Code_Size equ ((ROM_Size - 1)*512) OS_Code_Size16 equ ( OS_Code_Size / 2 ) Times (ROM_Size*512 - OS_Code_Size) - ($-$$) db 0 ;extend to 512 bytes, zero fill in between OS_Code:

Patching A64 Memory Timing through bios level

get the source code here:

http://www.xtremesystems.org/forums/...&postcount=384

Hi tictac.

1.)

How to build a BIOS module which is able to run this code:

http://www.farb-rausch.com/

-->

http://www.farb-rausch.com/fr026.zip

Code:; fr-026: 34b mul+cycle (uc 6.22 size optimizing compo entry) ; 1st place ; code: ryg (original concept) & kb (additional opcode crunching) ; ; rules were to write a "colorcycling" (no real colorcycling was ; required, only colorcycling-like animation) effect that display ; a x * y-ish pattern somewhere on the screen. the palette was ; required to look like the original version. org 256 mov al, 13h ; ...load al with 13h (mode number) int 10h ; set mode 13h mov bp, 320 ; screen is 320 pixels wide x les ax, [bx] ; es = end of mem (9fffh), ax = 20cdh cwd ; => dx = 0 (for idiv) mov ax, di ; get dest address idiv bp ; div by width => ax=y coord, dx=x coord imul dx ; mul x by y stosb ; store color in vram mov dx, 3c9h ; dac data bt cx, 6 ; bit 6 of cx => carry flag salc ; set al from carry flag xor ax, cx ; => all this is functionally equivalent to something like ; "test al, 64" / "jz skip" / "not al" / "skip: blah" ; which should be somewhat easier understandable, but bigger. out dx, al ; write grayscale pixel values out dx, al out dx, al loop x ; pixel loop. loop x ; skip cx = 0 to get the cycling effect! ; that's all there is to it. ; this is the 7th (or 8th) version; the first try was ; 49 bytes, from then on we successively made it smaller.

Well, I tried this...:

ASM:

HEX:Code:push bp stosb ; Store al to es:[di] mov al,13h int 10h ; Video display ah=functn 00h ; set display mode in al mov bp,140h loc_x: les ax,dword ptr [bx] ; Load seg:offset ptr cwd ; Word to double word mov ax,di ; Fixup - byte match ;* db 89h,0F8h ; Fixup - byte match idiv bp ; ax,dx rem=dx:ax/reg imul dx ; dx:ax = reg * ax stosb ; Store al to es:[di] mov dx,3C9h bt cx, 6 ; bit 6 of cx => carry flag salc ; set al from carry flag xor ax, cx ; => all this is functionally equivalent to something like ; "test al, 64" / "jz skip" / "not al" / "skip: blah" ; which should be somewhat easier understandable, but bigger. out dx, al ; write grayscale pixel values out dx, al out dx, al loop loc_x ; pixel loop. loop loc_x ; skip cx = 0 to get the cycling effect!

55AAB013CD10BD4001C4079989F8F7FDF7EAAABAC9030FBAE1 06D631C8EEEEEEE2E7E2E5

...and I used Bochs' feature to load Option/ISA ROMs.

But while booting Bochs with the compiled Option/ISA ROM,

there will be no switch to videomode 13h.

Bochs is still in text mode, but I can see sliding the colors of the background and the cursor.

2.)

Furthermore, how to insert a feature to break the animation

with any key

or

after a certain time?

3.)

How is it possible that "new" or nearly each todays BIOS's are able to display logos

in SVGA modes (640*480*256; 800*600*256; 1024*768*256; ...).

Do they already use VESA / VBE ?

BNOBTC & BNOBLG

Borg Number One's:

- BIOS Tool collection

- BIOS modifications

- BIOS Logo gallery

███████████████████████████████████████

http://bnobtc.pix-art.com

███████████████████████████████████████

Originally Posted by CodeRed

my antivir with latest definitions tells me that 0.31 (both files from that link) are infected with some trojan !!

Q6600 g0 L741 1.4V@35xx-> 8x44x FSB - 5:6 333/800- 2x2gb OCZ XTC Plats@53x mhz - dfi lp X38 TR2, Ultra Xtreme 120 - W7 64Bit - NV GTX275 - Corsair 520 (blew up) -> Toughpower 750W

wrote support email to the antivir people...this is something which REALLY annoys me since i cannot prevent the "found trojan" pop-up from coming up.

Q6600 g0 L741 1.4V@35xx-> 8x44x FSB - 5:6 333/800- 2x2gb OCZ XTC Plats@53x mhz - dfi lp X38 TR2, Ultra Xtreme 120 - W7 64Bit - NV GTX275 - Corsair 520 (blew up) -> Toughpower 750W

i deactivated the avguard

what do you think is more important? eh

thx @ codered amd supaguru

. . . WHO put this thing together? ME !

. . . WHO do i trust? ME !

. . . f*** it, as****

I checked V0.31. V0.50 and V0.60 Beta - AntiVir says all these Versions are infected by the Trojan Horse TR/Drop.VB.fk.2.1

But i guess the Detection is wrong, i've send the files to AntiVir. Addionally i found out when packing A64Tweaker with UPX and strip the Overlaycontent (Contains Debug-Infos, Paths and stuff), AntiVir doesnt alarm anymore.

If you want to continue using A64Tweaker with AntiVir, use this version -> http://rawhi.de/download/A64Tweaker_...ERLAYSTRIP.exe

Due the strpping and compressing its also only 176Kb (Original 516Kb).

Hi, can anyone assist me in finding which offset and bits to modify for the following options ?

Disable 32 Byte Granularity (A64Tweaker says its enabled, freezes when disabled)

Enable DRAM Bank Interleave (how do I check whether it's enabled or not ?)

I'd like to experiment with these options a little cause my board doesnt have them in BIOS and they'll probably won't add them in newer releases, so I'd like to patch them through bios level as per tic tac's A64 Bios Tweaker...

Any input will be greatly appreciated.

32 Byte Granularity :Originally Posted by ReelMonza

BUS - 0

DEVICE - 24

FUNCTION - 2

OFFSET - 90 (hex)

bit 19 ( 0 - disabled , 1 - enabled)

It works in combination with bit 16 (64 or 128 bit interface to DRAM), taken from AMD documentation:

Code:Bit 19 Bit 16 0 0 8-beat bursts (64 bytes) ------------------------------------ 0 1 4-beat bursts (64 bytes) ------------------------------------ 1 0 4-beat bursts (32 bytes) ------------------------------------ 1 1 4-beat bursts (64 bytes) 2-beat bursts (32 bytes) for Revision E and later revisions if Burst2Opt = 1, UnBuffDimm = 1, and En2T = 0 ------------------------------------

Bit 16:

128-Bit/64-Bit (128/64)—Bit 16. Indicates a 128-bit interface to DRAM.

0 = 64-bit interface to DRAM

1 = 128-bit interface to DRAM

Regarding DRAM Bank Interleave, it is not that easy, I will try to find out more.

I've played with DRAM interleave option in BIOS (DFI LP UT NF4 Ultra-D, 623-3 BIOS) and here is what I got. Just to mention, I have 2 sticks of PQI Turbo (2 x 512MB) in orange slots.

BUS 0, DEVICE 24, FUNCTION 2

32bit mode

Offset 4C

Eanbled

00001001 (hex)

Disabled

02000001 (hex)

Differences (enabled -> disabled):

Bit 12 (1 -> 0)

Bit 25 (0 -> 1)

Offset 68

Enabled

03E0EE00 (hex)

Disabled

01E0FE00 (hex)

Differences (enebled -> disabled)

Bit 12 (0 -> 1)

Bit 25 (1 -> 0)

Offset 6C

Enabled

03E0EE00 (hex)

Disabled

01E0FE00 (hex)

Differences (enebled -> disabled)

Bit 12 (0 -> 1)

Bit 25 (1 -> 0)

For more information see this (page 84):

http://www.amd.com/us-en/assets/cont...docs/26094.PDF

Looks like it is not that esasy to figure out. It would be interesting to see what happens with different configurations (1x512MB, 2x256MB, 1x256MB, different slots ....)

Hi, I enjoy using your a64 tweaker! I do have some questions:

1. how do you make windows load with startup settings? It doesnt work.

2. why does it sometimes default to loosest timing values? bug?

3. how do I change async latency in the bios of my gigabyte s939?

I am getting tired of manually changing it to 7 everytime windows loads cause the default of 6 isnt stable

3000+ Venice 240x9=2.16GHz(ondie controller limit) 2x512mb patriot tccd ram

9700pro at 325/310 runs all games buttery smooth!

9700(8 pipe softmod, 128m) at 410/325 23821 at 325/310 21287 at 275/270 19159

9500(4 pipes, 128m) at 420/330 18454 at 275/270 13319

9500(8 pipe softmod, 64m) at 390/310 19201 at 275/270 16052

9500(4 pipes, 64m) at 400/310 16215 at 275/270 12560

3dmark scores with Ti4200 and Ti4800se

Ti4200 at 340/730 19558 at 300/650 18032 at 275/550 16494 at 250/500 15295

3dmark scores with older gpus

Ti500 at 275/620 14588 Ti200 at 260/540 13557 MX440 at 380/680 11551

is there a guide for this a64 tweaker?

i'm kinda noob and don't know how to set it up for best performance...

X2 3800+ @2.4/1.45V Stock Cooling -- ABIT AN8 ULTRA --2x512 Corsair XMS3200C2PRO v4.3 -- GAINWARD 7800GT

"PLEASE HELP US MR. RED!"

Originally Posted by CodeRed

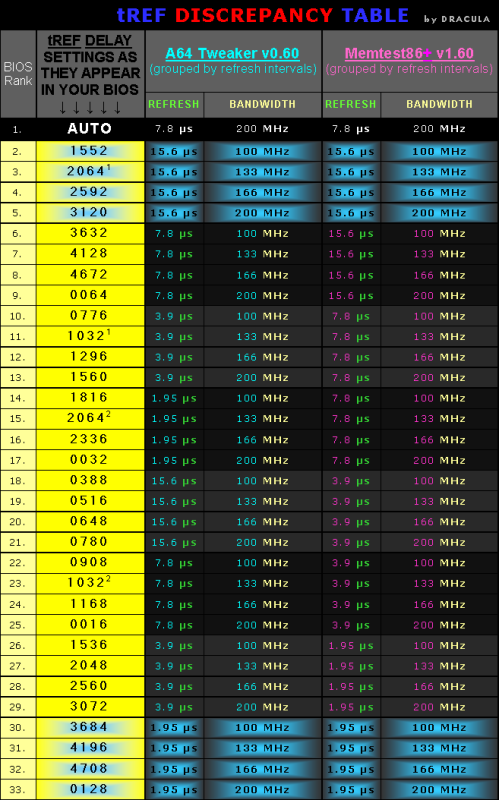

Code, I love this program you’ve created and I use it all the time, but there are many of us who are having a major issue concerning its accuracy versus the Memtest86+ v1.6 program. I came over here from the DFI-Street forum because we are fresh out of answers there. A specific debate is brewing as to which program, A64 Tweaker v0.60 Beta or Memtest86+ v1.6 (located in the BIOS of the DFI LANPARTY nF4 MoBos), is reading the tREF (click on the green tREF please) properly. Here are both the tREF Table and the tREF “Discrepancy” Table. I created them both and have posted them over at DFI-Street. A link to my tREF Table thread will be included in the tables themselves:

As you can clearly see on the tREF "Discrepancy" Table, the only two places where A64 Tweaker v0.60 Beta and Memtest86+ v1.6 agree, are in the highlighted blue sections. Now you can see why this is an issue. Not only because my tREF Table is based on your program, but because ALL the other simple tREF Tables, everywhere on the internet, are based upon your A64 Tweaker program. I cannot state, explicitly, that either program is wrong; I simply do not know the answer to this problem. There is, however, a British guy over at DFI-Street who keeps challenging the validity of my thread's claim because he professes to "know" that your program is wrong! He sites his belief that A64 Tweaker v0.60 Beta is invalid based solely upon the only “proof” he provides, which is that programs like RightMark Memory Analyzer, Central Brain Identifier and of course, Memtest86+ v1.6 all agree with each other, but disagree with your A64 Tweaker v0.60 Beta. I am not so quick to jump to this conclusion the way he is, however, because it is obvious to me that since all those "other" programs corroborate Memtest86+ v1.6, they are plainly reading the tREF data in the same manner. Given that A64 Tweaker v0.60 Beta is reading the tREF data differently than Memtest86+ v1.6, it obviously won't correspond with those other application's readings. Can you please help us by telling us which one is accurate and which one is in error and why, or if neither one is wrong, why there is this discrepancy? Thank you very much CodeRed

.

Last edited by GARM; 11-14-2005 at 02:37 AM.

GARM,

You know what? I have Asrock Satta II and just checked Everest and it shows 7.8 us for my Tref but all versions of A64 shows 3.9. I never noticed this until you brought this up. So therefore it is not just DFI mobo. And If Everest agrees w/ Memtest86, then I am guessing there is something wrong here (w/ A64 tweaker, hope not thu.)

I wish this issue is looked into by CodeRed or someone knowledgable w/ Tweaker's program and solve this problem.

Originally Posted by RimRam

Yes, I agree and I do believe that this is a real issue, but just so that everyone is crystal clear on this point, I did not bring this to your attention to be mean or a jerk-off critic. I did this to try and genuinely resolve the issue. Regardless of what is or isn't correct, or whatever the case may be, I think that A64 Tweaker is fantastic, as are programs like CBI and RMMA. I just hope that CodeRed looks into this for all of us. I also think that CodeRed is a great programmer too. Just so you know RimRam, to my knowledge, EVEREST only shows a refresh as is preprogrammed on your DIMM as it is reserved in the RAM's SPD. It is Memtest86+, Central Brain Identifier and RightMark Memory Analyzer that conflict directly with A64 Tweaker. EVEREST, like PC Wizard 2005, only displays the Serial Presence Detect, EEPROM that is right on your memory stick. The tREF I am concerned with is the one that can be adjusted in your BIOS on your MotherBoard. I also would like to point out that I know for fact that A64 Tweaker is 100% correct on all the other data it displays. The tREF is my only concern here.

I am now officially extending a request to ANYONE who may know the answer to this problem, or perhaps has a different spin on it, to let us know by posting a response in this thread. Until further notice and until this matter is cleared up satisfactorily, I shall display two versions of my tREF TABLE. One shall be based on Code's A64 Tweaker and the other on Memtest86+. I shall also include the tREF discrepancy Table between the other two and my TUTORIAL Table shall be exhibited at the bottom. Once this issue has reached an acceptable resolution, I shall remove the Table that displays incorrect data, should that be the case. Hopefully, there is someone out there who can assist all of us with this. Thank you! Peace...

bump?

...

Bookmarks