UPDATE: NEVERMIND! CLDO_VPP is more like the internal actual PHY voltage, and DRAM VDDP being the external reference voltage.

As per: https://community.amd.com/community/...lets-talk-dram

Which... damn! I wish I'd have been keeping up on the blog... They've provided all the juicy info I've been hoping to find!!

Oh right, duh, reason for coming here! Pfft lol I was going to pass along these two things...

First, a quote from The Stilt:

"tRC, tWR, tRDRDSCL, tWRWRSCL and tRFC are basically the only critical subtimings (for the time being).

Setting the SCL values to 2 CLKs basically makes no difference to the stability, but results in a nice performance boost.

Minimum tRC, tWR and tRFC depend on ICs and their quality.

tCWL adjustment is broken in AGESA 1.0.0.6 beta, but it makes pretty much no difference either."

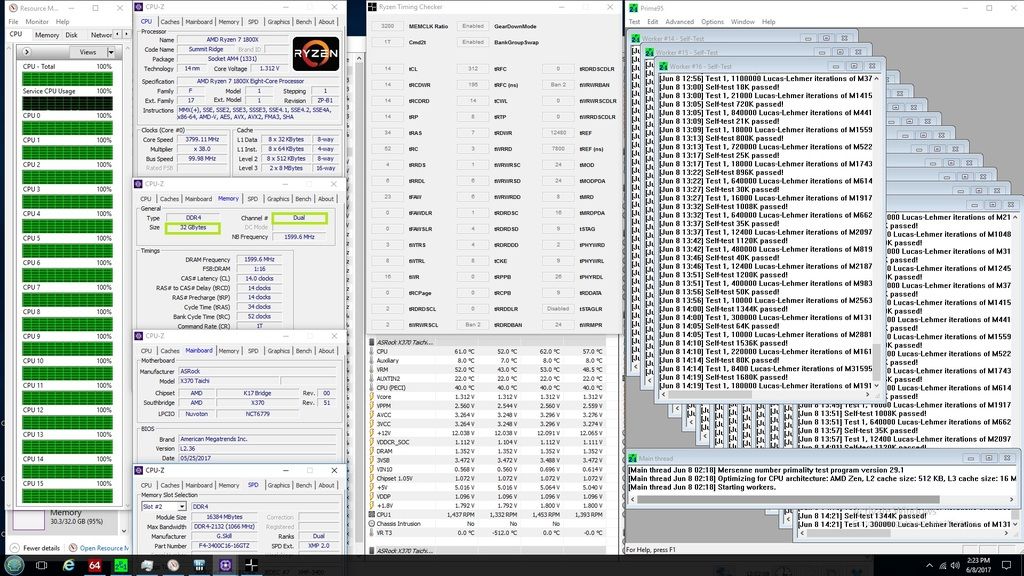

Second, a zero-overhead (non system polling) program by The Stilt, to read Ryzen timings. Figure it'll work a bit better than MemTweak for screenies

http://www.overclock.net/t/1624603/r...#post_26137022

"RTC (Ryzen Timing Checker)

Password: "RyzenDRAM"

x86-64 only.

Supports Zeppelin & Raven based Ryzens.

Let me know if (when) you find bugs."

Reply With Quote

Reply With Quote

Samsung LED 3D TV

Samsung LED 3D TV

On the plus side, the Cache stress, where I usually have the problems, went on for >11mins before I stopped it. Also had absolutely no problems playing Minecraft all yesterday or the day before, which laugh all you want, but at the tighter timings above, it crashed fairly often :P (I own a server so I am playing MC a lot for that reason, mostly spent 'babysitting' the teenagers that play.)

On the plus side, the Cache stress, where I usually have the problems, went on for >11mins before I stopped it. Also had absolutely no problems playing Minecraft all yesterday or the day before, which laugh all you want, but at the tighter timings above, it crashed fairly often :P (I own a server so I am playing MC a lot for that reason, mostly spent 'babysitting' the teenagers that play.) lol

lol

Bookmarks