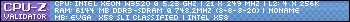

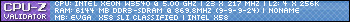

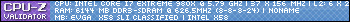

Well today Im launching a project... My HTPC is running following settings:

1.776v @ vdimm

1.1v VTT

According to XS, that should kill setup in matter of hours....

How long would ya like this to run, I bet it wont as much as damage a clarkdale....

Setup;

i5-650

Gigabyte GA-H57M-USB3

2x1GB D9GTR

133@160 bclk - 4ghz

2:10 (5x) - 800mhz 7-6-6-18

QPI: 2880*2 = 5760mhz (BCLK x36)

How long should this rig run in order to label it "myth busted".... And has to be on 24/7, or 4 hours a day for some months ok? : - )

Reply With Quote

Reply With Quote

Bookmarks