I was looking at the Intel datasheet for the Xeon 33xx series and ran into this section.

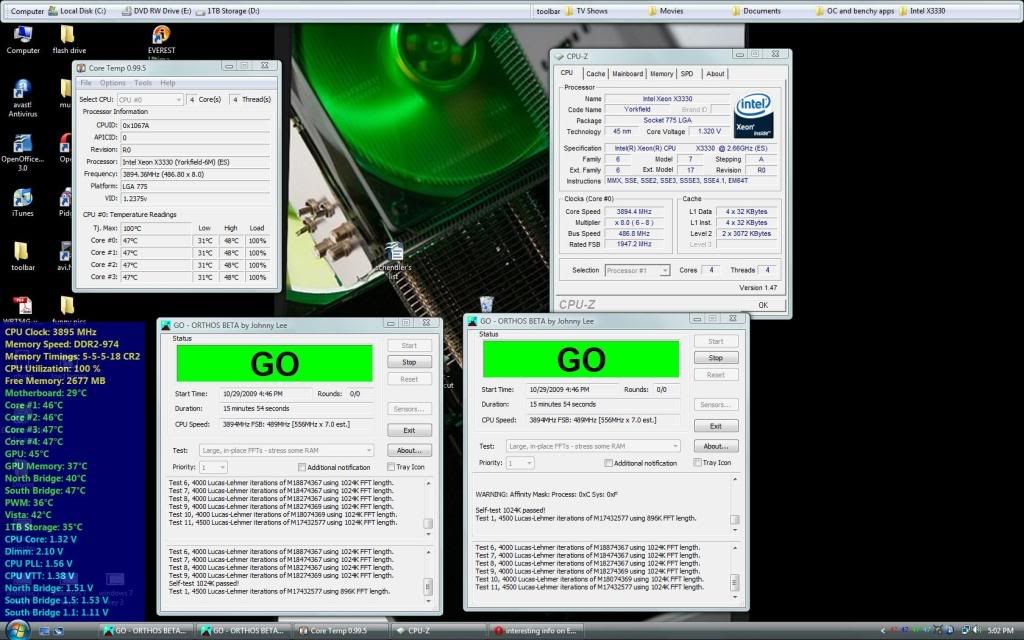

Does that mean, that if i had a custom written BIOS for my board that i could make available the ability to increase my multiplier? I'd love to see what the BIOS Writers Guide says if anyone could track down a copy.BCLK[1:0] directly controls the FSB interface speed as well as the core frequency of the processor. As in previous generation processors, the Yorkfield processor core frequency is a multiple of the BCLK[1:0] frequency. The processor bus ratio multiplier will be set at its default ratio during manufacturing. It will be possible for engineering samples to override this feature through the use of Model Specific Registers (MSRs) that are set through the BIOS. Refer to the Wolfdale Processor Family BIOS Writers Guide (BWG) for the details about these MSRs and the setting scheme of the core frequency to FSB multiplier ratios. The Yorkfield processor supports Half Ratios between 7.5 and 13.5, refer to Table 2-14 for the processor supported ratios.

Some processor engineering samples allow the core frequency to be configured by writing the desired core clock frequency to system bus ratio into bits [12:8] of the CLOCK_FLEX_MAX MSR. The BIOS must then initiate a CPU-only reset. After the CPU only reset, the processor will begin operating at the new core clock frequency to system bus ratio. Refer to the Wolfdale Processor Family BIOS Writers Guide (BWG) regarding details about this feature. Production processors will not support modification of this register since the required ratio is set during manufacturing. No user intervention is necessary, and the processor will automatically run at the speed indicated on the package.

The processor uses a differential clocking implementation. For more information on the processor clocking, refer to the CK505 Clock Synthesizer Specification.

Reply With Quote

Reply With Quote *

*

Bookmarks