According to some reviews a memory latency in pine-trail is a bit lower then in prev. gen. of atoms. But this doesn't affect performance since atom cores are too weak to utilize higher mem bandwidth/lower latency.

http://www.bit-tech.net/hardware/mot...way-mini-itx/4

The primary function of xbar is reordering memory queries from multiple cores. There was a good article about an intercore communications (C2D, Athlon64). All the syncs betwen L2 of a cores goes through the main memory.i thought they are hooked up to an internal switch? like the xbar between cores and imc on amds multi core cpus?

http://www.xbitlabs.com/articles/cpu...sis.html#sect0

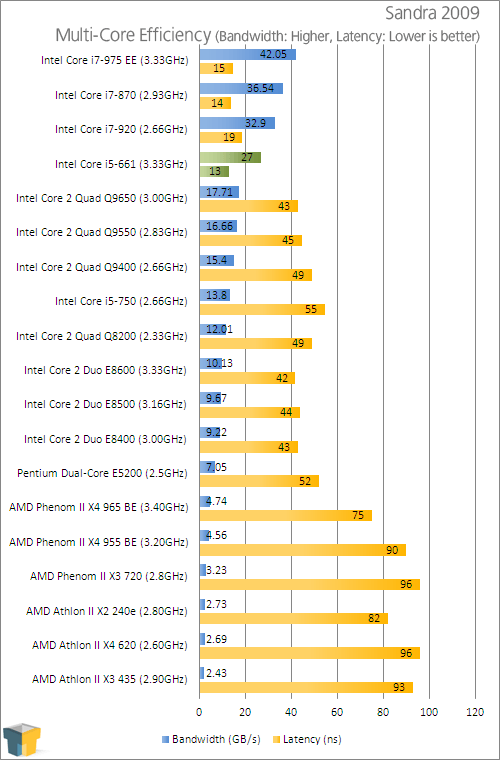

Even now an inter core efficiency in Phenoms is a weak point. Let see if they can fix it in upcoming llano.

Last edited by kl0012; 04-22-2010 at 05:11 AM.

But you have not said that the 2/4c sandy bridge is NOT a new, completely reworked microarchitecture, just that the 6/8 has even more (potential) changes.

The semiacc author is practically suggesting that 2/4 is a Westmere core bolted to a new uncore with GPU on die, oh, and, uh, plus AVX... or something.

Even Intel has now publicly said "significant IPC improvement" about the 2/4 parts. I don't think that means AVX.

http://download.intel.com/pressroom/...er_English.pdf

(pages 32,33)

http://news.cnet.com/8301-13924_3-20...orsPicksArea.0

Key points

While Intel Executive Vice President David Perlmutter said he would "not do a deep dive" on Sandy Bridge in his Intel Developer Forum Beijing keynote this week, he did reveal some key points about the architecture.

-More efficient: the central processing unit, or CPU, delivers a "significant improvement in instructions per clock," according to Perlmutter, meaning that it is more efficient at executing tasks.

-Faster on-chip communication: different parts of the chip will talk to each other faster--what Perlmutter called "improved inter-buses."

-Shared memory: on-chip memory called cache is shared between the CPU and graphics processing unit, or GPU.

-GPU now part of CPU: Intel combines the CPU and GPU on the same piece of silicon. According to an unofficial photo of the Sandy Bridge chip from Japanese Web site PC Watch, the GPU takes up roughly 25 percent of the processor's real estate.

-New instructions: Sandy Bridge will be the first chip to support Intel's Advanced Vector Extension (Intel AVX) instructions. AVX accelerates a host of multimedia tasks, including video and audio processing.

-More intelligent overclocking: and, finally, Perlmutter mentioned improved Turbo Boost--which speeds up (i.e., "overclocks") or slows down individual cores to meet processing or power efficiency needs.

Last edited by terrace215; 04-22-2010 at 10:13 AM.

Seems like a lower baseclock will allow for finer control of turboboost.

oh stop it, always teasing with all the things you know and then not telling anything :P

at least hint at whats wrong so i can try to find an answer somewhere else :P

oh come on guys! dont tell me i got it all wrong and its misleading and then leave me standing in the rain :P

at least hint at what was misleading... calling cache associativity cache width?

i wrote it, and thats not true about it?

where have they said that? and how would they achieve significant ipc improvements?

they havent mentioned anything that could potentially improve ipc significantly...

they ALWAYS say that for EVERY new cpu... they said that about nehalem as well and it ended up with almost the same ipc in most apps as c2d... :P

revamped cache, i mentioned that...

so reducing the L3 cache from 4 to 3mb and reducing it from 16way to 12way associative and THEN sharing it not only between 2 cores but the gpu as well... thats improving ipc how? :P

and that affects ipc how...? :P

new instructions will result in a boost in a few apps only at launch, if even that... i wouldnt count this as ipc boost, and you said you "heard" ipc improvements beyond avx, right?

this adjusts clocks, not ipc... so again, where are those ipc improvements intel supposedly raved about? :P

yeah, thats a good point... now its 100mhz steps and not 133 anymore... wont make a huge difference but should help a bit to maybe get higher turbo multis and lower idle clocks

i didnt read them, you quoted some info so i though that was the relevant info you were only linking there to provide a source...

let me read it now...

ok, the cnet article doesnt mention anything new, you had quoted the important parts, but they dont mention a significant ipc boost... at all...

the article mentions that sandybridge is intels most important design for the future... well yeah, like clarkdale was a few months ago

that doesnt mean itll be notably faster...

they demoed a laptop running "some" medical imaging program... they dont mention the performance, nor the name of the app, nor did they compare it to a clarkdale laptop to show a performance boost... so if you ask me, this sounds just like intel saying

a.) we got sandybridge up and running, see!

b.) its performing well

they dont mention improved performance vs clarkdale at all in that article...

lol, page 15 and following they make it look as if the different atom processors were entirely different chips

they are talking to engineers there at idf... do they really think they fall for this nonsense?

no mention of performance (besides avx)

improved ipc...

i see... so they did mention improved ipc...

they didnt mention improved performance though, and they dont mention "signficiantly improved ipc" as you said :P

improved ipc can mean many things... the revamped cache structure alone probably improves the ipc already... barely... but it does... so that would already count as an ipc improvement.

we will see, but i will be VERY surprised if there is a notable performance boost of sandbridge over clarkdale, besides gpu and avx, those might get a boost...

i should define what i mean by that though... even if sandybridge is 5% or even 10% faster than clarkdale at the same clockspeed, thats not a notable performance boost imo... thats not a reason to upgrade your laptop or pc, its like a mhz boost from 2000mhz to 2200mhz... thats nothing, you wont notice it...

but i dont expect even that, i think sandybridge will be 2% faster than clarkdale on average... the important points will be lower power consumption, more features (avx,better turbo,tweaked igp) and price...

I'll go even further and say IF intel manages an average of ~15% increase in IPC over same clocked(same turbo ability) clarkdale,than it's a success as far as the "significant IPC increase" story goes. Intel claimed,back in February,a 20% increase on unnamed workloads(may very well be a mix of computational and 2D/3D GPU heavy application),over same clocked arrandale/clarkdale chips.

I'm confused.

Is sandy bridge just a tweak/core upgrade from nehalem? With minimal clock/clock performance increase?

Like i7 was to Yorkfield, no improvement in realtime single core apps.

My emulators demand something newer than the performance levels of 6 year old chips. We are WAAAY overdue for a real increase.

pff, they claimed the same for clarkdale over wolfdale, actually way more, they claimed ~50% performance boosts back then... and for nehalem they did the same vs yorkfield... those are all best case scenarios...

come on, its not gonna happen... whats the last time we have seen a 20% ipc boost over a previous gen cpu? the original a64 did it and conroe did it, and they only managed that because the previous gen they used was outdated and sucked and the new arch was doing above average. and in both cases it was a mayor effort from intel and amd to get those new archs out. sandybridge is a small stepstone for intel, its not a mayor new arch...

wow, so many temp probes... and it can display the current power consumption? neat!!!

65W tdp? must be because its ES...

no turbo boost? same i guess... or maybe early bios?

lowest multi is 16x? and it cant drop every second clock to get down to 800mhz?

why are there two 3.3v readings?

whats vccp2? uncore?

itll have better turbo modes, hopefully, so that will help with single threadded apps... somewhat...

the next real ipc increase will be haswell, 22nm... thatll be a mayor step... and bulldozer from amd, which will probably come out first, but itll be on 32nm so even if its good intel should catch up pretty fast with haswell on 22nm...

on intels latest public roadmaps it shows sandybridge as the next step on 32nm right?

after that comes ivybridge at 22nm and then haswell at 22nm.

haswell is a really revamped architecture... sandybridge and ivybridge are just that, bridges, to that revamped arch...

they are all tweaks of the original Yonah archicture that replaced netburst.

Last edited by saaya; 04-23-2010 at 04:52 AM.

Shame though, my intel system is already at 4ghz. If turbo is the only major increase then I'm already doing it manually.

So, Haswell vs Bulldozer. I've heard the name bulldozer bantered about since I joined xs ....many years ago. I assumed it was an ancient architecture of the P3 era. Must have been the AMD forum clutching at straws over the failure of phenom 1.

bulldozer has been in the works since before conroe came out, possibly much longer than that... so thats... 2005 or earlier... but what they originally planned as bulldozer is very very different from what they are going to actually release...

i remember reading an interview at anandtech with some higher up at amd about half a year before conroe came out, that their arch was good enough and that for the next few years they would only bump the clocks up and that would be enough... i had a very bad feeling about amd back then lol...

Last edited by saaya; 04-23-2010 at 05:22 AM.

TDP and Turbo are correct for this one. Reason: Early Sample

Don't count on those Nuvoton NCT6771F sensor values, these are just generic outputs that need to be adjusted per a specific mobo (like all sensors on each mobo). Since this mobo is a pretty early sample, I'm not sure if I will be able to adjust them now.. Will see...

Originally Posted by saaya

Will post a similar screen of quad sandy bridge soon "Later today or day after" depending upon when i get the screens from a guy.

Coming Soon

probably not worth it to adjust them then... the final boards will be different, even the intel ref boards that end up in retail will probably be different...

thanks!

mhhh anandtech is too mainstream... i dont think intel will ask them to publish a sandybridge preview anytime soon... especially since the target is mobile, and for that perf/watt is everything and i highly doubt they have that tweaked to a level yet that would look notably better than arrandale let alone culv... so that wouldnt be too smart for intel to show off... i wouldnt be surprised if jarred has a sample or will get one soon, or maybe johan/anand have a 6core or 8core sample now or soon... but i doubt they will be allowed to write about it...

I wanted to correct and clarify some of the conjecture here:

Sandy Bridge is a new µArch. It is not a tweak of Nehalem. Westmere was a tweak of Nehalem. Whether or not there are "major" changes in IPC from Nehalem remains to be seen. Most of you think that it's not likely to be a huge IPC gain and I tend to agree. Regardless, it is an Intel "tock" which brings a new µArch to an established process node: 32nm.

CPU: Intel i7 3770k. . . . . . . .Cooler: CoolerMaster Hyper 212 Plus

Mobo: ASUS P8Z77-V Deluxe . . . . RAM: 4x4GiB GSkill Rampage 2133MHz 1.65V

Video: Sapphire Radeon 7970 . . . Drives: Intel 520 SSDs

Power: Seasonic Platinum 860W. . .Case: Rosewill Thor v2

I'll try to speak S L O W L Y for you.

The cnet article quotes (you know QUOTATION MARKS?) perlmutter from his presentation. You know, he was on a stage. He was speaking. The audio/video presentation is still available along with the slide deck. He said "significantly improved IPC". C L E A R ?

How could this happen in a completely reworked microarchitecture? Oh, I dunno. L1 latency going from 4 to 3 cycles might help.

But I see. 10% is now not significant. At least you are on the record with your 2% prediction.

Yes there is.

The architecture carries a new power regulation scheme.

Even if the socket is identical you will need a new chipset. A BIOS flash will not suddenly give you a new chipset.

This is now public knowledge, having been published by VR-Zone:

http://vr-zone.com/articles/a-look-i...ay/8877-3.html

(I haven't waded through the entire thread, sorry if people have already mentioned this.)

yes, its a tock, i know... new µarch, well thats almost a marketing term this days, isnt it?

if there is a lot of really new stuff in sandybridge intel sure has kept quiet about it... id love to be surprised in a good way... so im looking forward to some benchmarks in the following weeks

this is a F O R U M! people here communicate by W R I T I N G messages, you can speak as slowly and clearly as you want, i wont hear you

can we stop this? this is really childish man... please...

you need to reset your sarcasm, its way overloaded...

yes, and at least years idf in taipei somebody said nehalem will heal cancer... cause its oh so fast at medical scientific calculations... like i said, they always make wild claims about their newest cpu... intel told system builders to not expect a major performance boost until haswell... they even had a slide about it in a semi public presentation to analysts... but i couldnt find it on anymore googling for it...

so you think dropping the L1 latency by 25% will result in a 10% performance boost?

i dont think the chipset is that important... they could make the new cpus work with the old chipset easily i think... as a matter of fact the "new" chipsets arent really new, they have barely been modified from the current ones...

its all about the igp data and pwm protocoll as far as i know...

Last edited by saaya; 04-23-2010 at 10:36 AM.

If you have read the article... Sigh nevermind. Here, I'll quote it right here. This is what they wrote:

Even though they were specifically talking about the extreme platform, I wouldn't be surprised if the rest of the line work the same way.VR12 will use a 25MHz 3wire serial interface for Serial VID (SVID). VR12 will offer SVID steps with 5mV resolution opposed to VR11.1's 6.25mV resolution (using a 8-bit VID table).

Again, a BIOS flash is not going to give you a whole new regulation scheme. It requires hardware change.

Others in the thread have also mentioned power savings this new scheme enables. You also need new hardware for this, and it's probably not just at the bare chip level either. A BIOS flash isn't going to change that piece of PCB the chip rests on, either.

Bookmarks